利用SoC平台设计并验证MPEG-4/JPEG编解码IP

[10-10 20:36:41] 来源:http://www.88dzw.com 电子制作 阅读:8491次

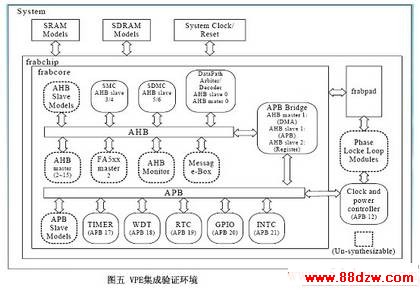

文章摘要:智原科技 starcells仿真模型(sdmc, gpio, smc …. ) 其它相关器件仿真模型(sdram/ rom/ I/O model )设计者可以根据需要添加自己的设计,例如挂在AHB上的MPEG4编解码器。每一个功能模块都可以在VPE中独立仿真。智原科技可在VPE上提供了AMBA的各个功能模块的仿真模型,设计者可以很方便的搭建起一个基于AMBA的SoC系统并进行测试。其VPE的仿真模型包括下列:行为级模型(Behavioral Model)-AHB 主器件(Master)-AHB 从器件(Slave)-AHB 监视器(Monitor)-APB 从器件(Slave)RTL 级模型-

利用SoC平台设计并验证MPEG-4/JPEG编解码IP,标签:电子小制作,http://www.88dzw.com智原科技 starcells仿真模型(sdmc, gpio, smc …. )

其它相关器件仿真模型(sdram/ rom/ I/O model )

设计者可以根据需要添加自己的设计,例如挂在AHB上的MPEG4编解码器。每一个功能模块都可以在VPE中独立仿真。智原科技可在VPE上提供了AMBA的各个功能模块的仿真模型,设计者可以很方便的搭建起一个基于AMBA的SoC系统并进行测试。其VPE的仿真模型包括下列:

行为级模型(Behavioral Model)

-AHB 主器件(Master)

-AHB 从器件(Slave)

-AHB 监视器(Monitor)

-APB 从器件(Slave)

RTL 级模型

-仲裁器(Arbiter)

-解码器(Decoder)

-有直接存储器存取(DMA)通道的AHB-to-APB桥接器

-没有直接存储器存取(DMA)通道的AHB-to-APB桥接器

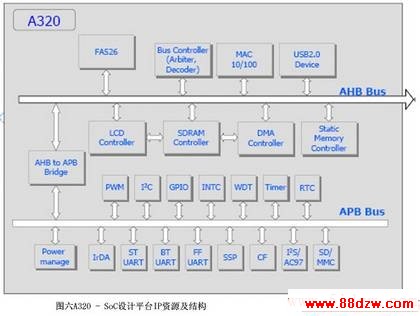

完成了功能仿真后,我们利用如图六所示A320的SoC设计平台做FPGA硬件仿真,A320集成了完成设计所需的IP。用FPGA实现的逻辑模块通过AHB/APB总线连接器与A320设计平台连接,可以很方便地完成功能验证,调试等一系列动作。因为A320芯片上的IP均为硅验证,在验证设计的同时也保证了从设计到芯片的一致性。

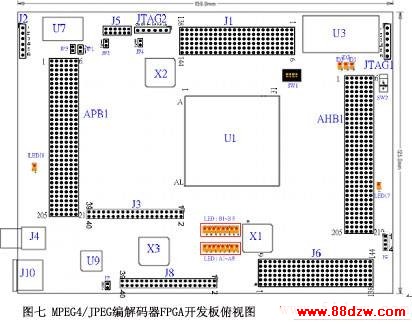

我们设计了一款能与A320进行验证的FPGA开发板,如下图七所示。MPEG4/JPEG编解码器开发板包括Xilinx Virtex-II XC2V4000 BF957, 视频捕获和A320接口。他提供了板上FPGA (XC2V4000 BF957),SAA7113 视频捕获芯片,CMOS传感器模块,16个LED用以显示调试的信息,2个扩展总线和一个AHB连接器连接A320开发板。我们也制作文档说明Pin脚的定义,方便使用者理解设计原理。

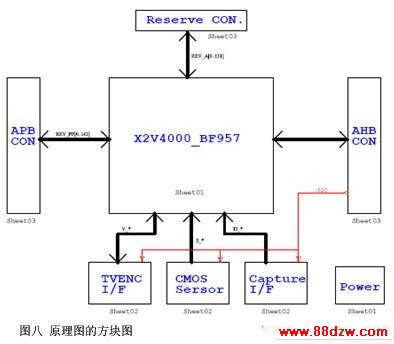

我们也提供原理图给使用者,如下图八所示,使用者可完全理解讯号流的走向。

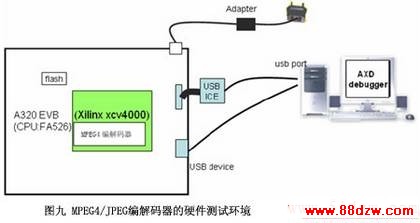

我们的测试环境很方便,如下图九所示,利用ARM的软件开发环境, 智原科技或ARM所提供USB接口的ICE调试开发板,将上述的MPEG4/JPEG 编解码器FPGA开发板插入A320的AHB与APB总线连接器后,将A320上电,PC使用USB口连接A32开发板。在MPEG4或JPEG 编码模式下,AXD调试器用以下载图像数据以及运行韧件,随后MPEG4/JPEG编解码器压缩图像数据。压缩的数据流需要被储存起来成为最后的压缩档。在MPEG4或JPEG 解码模式下, AXD调试器以下载压缩的数据流以及运行韧件,随后MPEG4/JPEG编解码器解压缩数据。

- 上一篇:多功能限电保护器

《利用SoC平台设计并验证MPEG-4/JPEG编解码IP》相关文章

- › 利用SoC平台设计并验证MPEG-4/JPEG编解码IP

- 在百度中搜索相关文章:利用SoC平台设计并验证MPEG-4/JPEG编解码IP

- 在谷歌中搜索相关文章:利用SoC平台设计并验证MPEG-4/JPEG编解码IP

- 在soso中搜索相关文章:利用SoC平台设计并验证MPEG-4/JPEG编解码IP

- 在搜狗中搜索相关文章:利用SoC平台设计并验证MPEG-4/JPEG编解码IP

当前位置:

当前位置: