布尔逻辑的应用

[09-12 12:22:25] 来源:http://www.88dzw.com 电路基础 阅读:8294次

文章摘要:R S Q Q' 0 0 非法 0 1 1 0 1 0 0 1 1 1 记忆 从逻辑表可以看到: 如果R和S的状态相反,则Q与S相同,且Q'与Q相反。 如果R和S同时切换为1,则电路会记住R和S上先前显示的内容。 有趣的是,该逻辑表中还有一种非法状态。在这种状态下,R和S都为0,在此状态下没有记忆值。由于存在非法状态,因此通常要在输入端添加一些条件逻辑以防止出现这种状态,如下图所示: 在该电路中,有两个输入(D和E)。您可以将D视为“数据”,并将E视为“启用”。如果E为1,则Q的状态将与D相同。但是如果E更改为0,则Q将会记住在D上最后看到的内容。以这种方式运行的电路通常称为

布尔逻辑的应用,标签:电子电路基础,模拟电路基础,http://www.88dzw.com| R | S | Q | Q' |

| 0 | 0 | 非法 | |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 记忆 |

从逻辑表可以看到:

- 如果R和S的状态相反,则Q与S相同,且Q'与Q相反。

- 如果R和S同时切换为1,则电路会记住R和S上先前显示的内容。

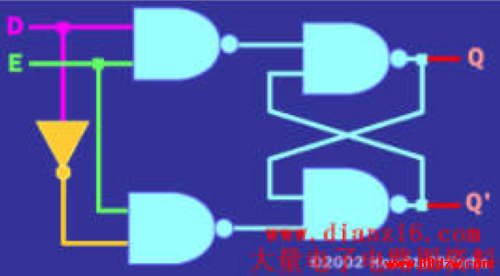

有趣的是,该逻辑表中还有一种非法状态。在这种状态下,R和S都为0,在此状态下没有记忆值。由于存在非法状态,因此通常要在输入端添加一些条件逻辑以防止出现这种状态,如下图所示:

在该电路中,有两个输入(D和E)。您可以将D视为“数据”,并将E视为“启用”。如果E为1,则Q的状态将与D相同。但是如果E更改为0,则Q将会记住在D上最后看到的内容。以这种方式运行的电路通常称为触发器。

触发器的一种常见形式是J-K触发器。人们并不清楚“J-K”名称的历史来由,但通常它会出现在一个黑盒子中,如下所示:

在该示意图中,P代表“预设”,C代表“清除”,Clk代表“时钟”。该逻辑表如下所示:

| P | C | Clk | J | K | Q | Q' | |

| 1 | 1 | 1到0 | 1 | 0 | 1 | 0 | |

| 1 | 1 | 1到0 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 1到0 | 1 | 1 | 切换 | ||

| 1 | 0 | X | X | X | 0 | 1 | |

| 0 | 1 | X | X | X | 1 | 0 |

该表表明:首先,“预设”和“清除”完全覆盖J、K和Clk。因此,如果“预设”变为0,则Q将变为 1;如果“清除”变为0,则Q将会变为0(不管J、K和Clk执行何种操作)。但是,如果“预设”和“清除”都为1,则J、K和Clk均可执行。1到0符号表示时钟从1更改为0时,如果J和K的状态相反,则将记住J和K的值。在时钟的下降沿(从1到0的转换),将存储J和K。但是,如果J和K在下降沿上正巧都为1,则Q只能切换。也就是说,Q将从当前状态变为相反的状态。

上一页 [1] [2] [3] [4] [5] [6] [7] 下一页

Tag:电路基础,电子电路基础,模拟电路基础,电路基础

- 上一篇:操作系统工作原理

《布尔逻辑的应用》相关文章

编辑推荐

分类导航

最新更新

- ・ 什么是系统仿真

- ・ 什么是CPCI

- ・ 英特尔 Parallel Composer入门

- ・ 什么是支持数据库,什么是中宏数据库

- ・ 什么是数据交换技术

- ・ 什么是内部数据传输率

- ・ 什么是空间数据交换中心

- ・ 什么是差异备份

- ・ 什么是备份集

- ・ 什么是映像备份

热门排行

- ・ IGBT模块

- ・ 什么是24脉波整流变压器

- ・ 自动变速器不能强制降挡故障原因、诊断与排

- ・ 什么是MD机

- ・ 中心频率,什么是中心频率

- ・ 功率单位mw和dbm的换算表

- ・ 中值滤波模块设计思路

- ・ 反馈振荡器的原理

- ・ 气体激光器简介

- ・ 数制与进位记数法

当前位置:

当前位置: