基于TMS320VC550的JPEG视频压缩系统的实现

[09-14 01:15:34] 来源:http://www.88dzw.com 电子制作 阅读:8941次

文章摘要:6.2 压缩耗时实验结果对于一个8x8数据块,各步耗时如下:分块:1.335μs;DCT变换:5. 39μs;量化:1.355μs;哈夫曼编码:3.375μs。说明一个8x8数据块总耗时为11.455μs,一帧720x576灰度图像的压缩总耗时为90x72x11.455=74 228.4μs,再加上其他辅助操作,实际耗时约75 ms。根据上述结果,在1 s内向上位机发送13帧720x576的灰度图像,基本满足系统要求。7 结束语介绍基于TMS320VC5509A DSP的JPEG视频压缩系统的设计和实现方案,该系统硬件设计采用DSP+FPGA的方案,充分发挥了各自优势;而软件设计针对C55x的

基于TMS320VC550的JPEG视频压缩系统的实现,标签:电子小制作,http://www.88dzw.com

6.2 压缩耗时实验结果

对于一个8x8数据块,各步耗时如下:分块:1.335μs;DCT变换:5. 39μs;量化:1.355μs;哈夫曼编码:3.375μs。说明一个8x8数据块总耗时为11.455μs,一帧720x576灰度图像的压缩总耗时为90x72x11.455=74 228.4μs,再加上其他辅助操作,实际耗时约75 ms。根据上述结果,在1 s内向上位机发送13帧720x576的灰度图像,基本满足系统要求。

7 结束语

介绍基于TMS320VC5509A DSP的JPEG视频压缩系统的设计和实现方案,该系统硬件设计采用DSP+FPGA的方案,充分发挥了各自优势;而软件设计针对C55x的结构进行程序结构和算法优化,经过验证达到较好的实时效果。由于该系统体积小、功耗低,适用于一些野外图像采集、远程视频监控等需要连续传输图像的场合。

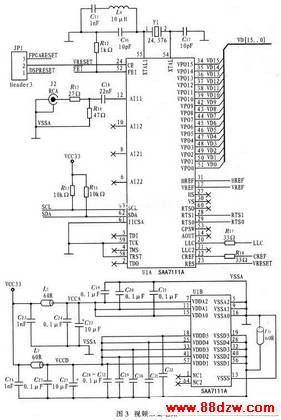

www.88dzw.com3.1 视频采集电路

该系统选用的视频解码器为Philip公司的高性能视频A/D转换器SAA7111。该器件是一款广泛应用于桌面视频、多媒体、数字电视、图像处理、视频电话的高性能视频输入处理器件。该器件采用3.3 V的CMOS电路,高度集成模拟前端和数字视频编码器;包括2路模拟视频处理通道,1个时钟产生电路,1个自动箝位和自动增益控制电路,1个多制式数字解码器,1个亮度/对比度/饱和度控制电路,以及色彩空间矩阵。SAA7111输出为16位VPO总线,支持不同位宽的数据输出格式。SAA7111支持的输出格式包括:12位YUV411,16位YUV4:2:2,8位CCIR-656、16位565RGB以及24位的888RGB。图3为视频采集电路。

3.2 存储器选型

选择存储器应从以下方面考虑:首先图像压缩算法中间数据量大,要求处理器的片上内存尽可能大,尽量避免对外部存储器读写操作。VC5509A的片上存储器包括32 Kx16位DARAM,96 Kx16位SARAM,共128 K位的存储空间。其中DARAM为双地址,在每个周期内可以对其进行两次操作(2次读,两次写,一次读和一次写),这样大大增加片上存储器的利用率;其次,VC5509A片上资源丰富,包括I2C总线(多主从接口),3个McBSPs(1个与多媒体卡/数字加密卡MMC/SD串行接口复用引脚)。利用 FC总线对SAA7111的片内控制寄存器进行读写操作,非常方便实时控制SAA711 1的工作状态;利用McBSP配合DMA,软件编程实现UART功能,无需专门的硬件UART,从而节省电路板空间:VC5509A采用144引脚 LQFP封装,便于安装、调试;VC5509A功耗小,工作在200 MHz主频下,功耗仅100 mW,非常适合嵌入式应用。

《基于TMS320VC550的JPEG视频压缩系统的实现》相关文章

- › 基于TMS320VC550的JPEG视频压缩系统的实现

- › 基于TMS320C6713的多路CVSD语音编解码

- › 基于TMS320VC5409的水声通信Modem设计与实现

- 在百度中搜索相关文章:基于TMS320VC550的JPEG视频压缩系统的实现

- 在谷歌中搜索相关文章:基于TMS320VC550的JPEG视频压缩系统的实现

- 在soso中搜索相关文章:基于TMS320VC550的JPEG视频压缩系统的实现

- 在搜狗中搜索相关文章:基于TMS320VC550的JPEG视频压缩系统的实现

编辑推荐

- ・ 自制教室照明节电控制器

- ・ 双色音乐彩灯的制作

- ・ 三相交流电机缺相保护器

- ・ 声光控节能灯的制作

- ・ 同线电话转呼及互通器电路

- ・ 超低频信号发生器的制作

- ・ 自制热转印电路板

- ・ 警笛发声生器电路

- ・ 一款节能电路

- ・ 利用太阳能充电的旅行充电器

当前位置:

当前位置: