高清视频CMOS电流舵数/模转换器的设计

[10-10 20:42:03] 来源:http://www.88dzw.com 电子制作 阅读:8651次

文章摘要:5 实验结果 该文设计的DAC基于O.25 μm CMOS技术,8位高速DAC适用于高清晰视频使用,并且使用TG晶体管和电路级数的数量可以明显减少,同时使用TG结构也可使电路延迟时间有效地减少,且毛刺也被大大减少。结果显示:这个设计可以达到1.5 GHz采样率和21 mW低功耗。 具体参数指标如表2所示。6 结 语 本文提出基于新型传输门(TG)结构组成的电流源单元矩阵、译码逻辑电路和一种适用于高清晰视频使用的高速8位CMOS电流舵数/模转换器(CS- DAC)。应用电流源单元矩阵结构和传输门结构的译码电路能有效减少毛刺等干扰信号;采用TG结构设计的电路,可使晶体管数量和电路

高清视频CMOS电流舵数/模转换器的设计,标签:电子小制作,http://www.88dzw.com5 实验结果

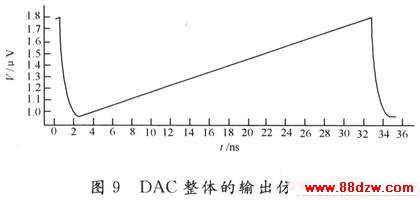

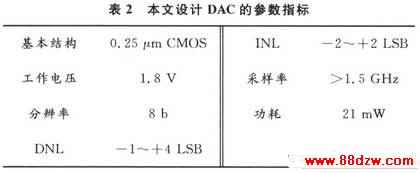

该文设计的DAC基于O.25 μm CMOS技术,8位高速DAC适用于高清晰视频使用,并且使用TG晶体管和电路级数的数量可以明显减少,同时使用TG结构也可使电路延迟时间有效地减少,且毛刺也被大大减少。结果显示:这个设计可以达到1.5 GHz采样率和21 mW低功耗。

具体参数指标如表2所示。

6 结 语

本文提出基于新型传输门(TG)结构组成的电流源单元矩阵、译码逻辑电路和一种适用于高清晰视频使用的高速8位CMOS电流舵数/模转换器(CS- DAC)。应用电流源单元矩阵结构和传输门结构的译码电路能有效减少毛刺等干扰信号;采用TG结构设计的电路,可使晶体管数量和电路的延时显著减少;基于 0.25μmCMOS技术的DAC电路设计,功耗仅为21 mW,采样率达到1.5 GHz。仿真结果表明,电路的积分线性误差(INL)范围为-2~+2 LSB,微分线性误差(DNL)为-1~+4 LSB。

图2是一个说明8位分段式电流舵基本结构的例子。图中采用6+2分段结构,高6位数字信号通过行译码器(Rows Decoders)、列译码器(Columns Decod-ers)转换为温度计码,分别控制26-1=63个单位电流源,构成8×8电流源矩阵。多余的一个电流源作为Dummy器件,63个单位电流源和低2位二进制加权电流源的电流之和形成了阵列中整体电流源的电流。

2 译码逻辑电路

在DAC设计中,电流源单元、译码器和消除毛刺(噪声)结构是重要部分,DAC的性能由这些部分决定。为了改进在高频率动态线性,在此提出由传输门和晶体管组成组合逻辑译码电路。

2.1 传输门逻辑

因为NMOS管可以通过逻辑变量0传输,PMOS管可以通过逻辑变量1传输,用这两个MOS平行放置构成互补结构。在此,可以得到传输门(TG),并且对于TG,逻辑变量0,1都可以很好的传输。大家都知道,译码器之间的延迟时间是毛刺发生的主要原因,并且与全部使用CMOS逻辑电路比较,用TG设计的逻辑电路性能更好,延迟更小。经过验证,所有二输入逻辑门的可由传输门和反相器组成。作为一个事例,实现与非门逻辑,全部CMOS技术要求6只晶体管,但采用TG结构只需要5只晶体管。在内在DAC芯片上,它有两个信号,并且有翻转信号,因此没有反相器的需要,因而二只晶体管被减少。实验结果说明,芯片面积和功耗的大大减少了。

2.2 逻辑译码电路

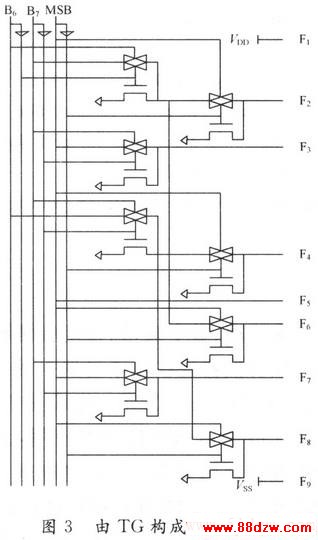

为减小功耗和减少延时,应该设计最少逻辑水平的行和列译码,运用TG逻辑电路组成3~8位行、列译码器。如此从高3位得到行译码器和从中间3位输入得到列译码器。运用TG的行译码器电路如图3所示。

行译码器结构与列译码器基本相同,但没有电源节点。使用TG逻辑译码器的另一巨大好处是可以减少晶体管的数量。在静态逻辑,参考文献[9]的译码器由84 只晶体管组成,但用TG结构组成的行和列译码器有30只晶体管,并且总数是60。这意味着芯片面积可能也被减少。较少的晶体管级数也帮助减少延时。另一方面,使用TG结构的逻辑门最大级数可减少到2级;不使用传输门结构的全CMOS结构的最高门级数是3,以上充分说明使用TG结构更有利减少延时和改进工作频率。表1给出相关的参量对比。

- 上一篇:新型声码器CMX638及应用设计

《高清视频CMOS电流舵数/模转换器的设计》相关文章

- › 高清视频CMOS电流舵数/模转换器的设计

- › iPad支持(能看)高清视频电影吗

- › 高清视频播放器与HTPC哪个好

- › ThinkPad R61i能否看高清视频

- › 老无线路由器无法下载高清视频

- 在百度中搜索相关文章:高清视频CMOS电流舵数/模转换器的设计

- 在谷歌中搜索相关文章:高清视频CMOS电流舵数/模转换器的设计

- 在soso中搜索相关文章:高清视频CMOS电流舵数/模转换器的设计

- 在搜狗中搜索相关文章:高清视频CMOS电流舵数/模转换器的设计

当前位置:

当前位置: