USB的便携式ARINC429总线通信设备设计

[09-14 00:27:48] 来源:http://www.88dzw.com 通信电路 阅读:8160次

文章摘要:摘要:基于Actel公司的ProASIC3系列FPGA和Silicon Labs公司的C8051F340单片机设计了一种便携式ARINC429总线通信设备,着重介绍了整体设计思想以及软硬件设计方法。该设备具有性能可靠、携带方便、成本低廉等特点,可广泛应用于对各种以ARINC429总线作为通信方式的机载设备的通信测试及地面检测维护。关键词:FPGA;USB;ARINC429;通信测试;C8051F340;ProASIC3 在航空电子综合化系统中,快速、有效的数据传输对整个航空电子系统的性能有很大影响,因此数据总线被称为现代航空电子系统的“骨架”。ARINC429是航空电子系统之间最常用的通

USB的便携式ARINC429总线通信设备设计,标签:电路设计,http://www.88dzw.com摘要:基于Actel公司的ProASIC3系列FPGA和Silicon Labs公司的C8051F340单片机设计了一种便携式ARINC429总线通信设备,着重介绍了整体设计思想以及软硬件设计方法。该设备具有性能可靠、携带方便、成本低廉等特点,可广泛应用于对各种以ARINC429总线作为通信方式的机载设备的通信测试及地面检测维护。

关键词:FPGA;USB;ARINC429;通信测试;C8051F340;ProASIC3

在航空电子综合化系统中,快速、有效的数据传输对整个航空电子系统的性能有很大影响,因此数据总线被称为现代航空电子系统的“骨架”。ARINC429是航空电子系统之间最常用的通信总线之一。要在计算机上实现与机载设备的ARINC429总线数据通信,必须实现429总线与计算机总线之间的数据传输。本文设计了基于USB总线的便携式ARINC429总线通信设备,并通过实际运行测试,对该设备的可靠性和稳定性进行了验证。

1 系统总体设计

1.1 系统功能分析

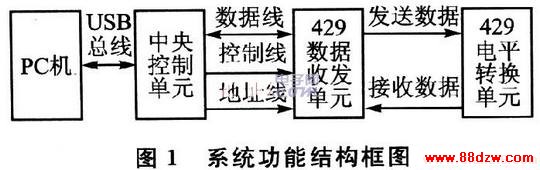

该系统主要分为3大功能单元:中央控制单元、429数据收发单元、429电平转换单元。系统的功能结构框图如图1所示。中央控制单元与PC机进行USB通信,将USB总线转换为自定义总线,并根据PC机发来的任务指 令,通过自定义总线(数据线、地址线、控制线)控制429数据收发单元完成相应的429总线数据收发任务。

1.2 主要器件选择

1.2.1 中央控制单元

中央控制单元负责与PC机进行USB通信,并控制429数据收发单元完成通信工作。该单元采用SiliconLabs公司推出的C8051F340单片机。它是完全集成的混合信号SoC级MCU芯片,片内集成有1个采样率为200Ksps的10位ADC、1个可编程增益放大器、2个电压比较器、1个电压基准、1个具有5个捕捉/比较模块的可编程计数器/定时器阵列(PCA)、5个通用的16位定时器、40个通用数字I/O端口,以及1个片上64 KB的Flash存储器和4 KB的RAM,支持多种总线通信接口(I2C/SMBus、SPI、UART、USB)。C8051F340的最大指令处理速度为48 MIPS,具有片内VDD监视器、WDT和时钟振荡器,能有效地管理模拟和数字外设。

C8051F340最大的优势是在片内集成了一个USB总线控制器,与USB2.O完全兼容,支持低速和全速两种模式。这样,在硬件上只需一片C28051F340就能与PC机直接进行USB通信,无需外加USB接口芯片。

1.2.2 429数据收发单元

目前市面上的429通信专用芯片(如HS-3282、DEI1016、HI-8585)只能实现1路发送或接收,要满足本设计需求就需要8组429通信专用芯片(共计16片)。无论从成本上,还是从设计本身的可行性、可靠性来考虑,都是难以实现的。本文采用Actel公司的ProASIC3型FPGA,将设备的核心部分――429通信协议模块在FPGA中实现。这样使整体设计更加简洁,充分体现了模块化设计和SoC设计思想,同时大大降低了设计成本。

Actel公司的ProASIC3型FPGA采用独一无二的Flash架构。与基于SRAM架构的FPGA不同,它掉电后数据不易失,无需配置芯片,从而实现了真正意义上的单芯片设计思想。同时,它支持FlashLock、AES加密技术,安全性强;最高支持350 MHz单端翻转率和700 MHz的差分信号;支持19种I/O电平标准。

3.1 ProASIC3内核设计

ProASIC3内核开发是在Amel公司提供的LiberoIDE 8.5集成开发环境下完成的。该环境集成了目前业界最权威的几大FPGA开发软件,其中综合工具采用了Synplify公司的Synthesis 9.6A工具,仿真工具采用MentorGraphic公司的Modelsim 6.4A软件。整个设计采用Verilog语言编程。ProASIC3内核的总体框架设计如图4所示。ProASIC3内核设计包括收发控制器、发送FIFO、接收FIFO、发送逻辑转换模块、接收逻辑转换模块、时钟发生器模块。收发控制器负责与C8051F340进行总线通信,协调ProASIC3内部各个模块之间的工作;发送FIFO用于缓存待发送的429数据;接收FIFO用于缓存待读取的429数据;发送逻辑转换模块是将发送FIFO送来的并行数据组合为429串行数据,然后通过端口TXA、TXB发送出去;接收逻辑转换模块是将收到的429串行数据转换为并行数据,然后通过8位数据线传给接收FIFO;时钟发生器是用于产生各个模块所需的工作时钟。

《USB的便携式ARINC429总线通信设备设计》相关文章

- › USB的便携式ARINC429总线通信设备设计

- 在百度中搜索相关文章:USB的便携式ARINC429总线通信设备设计

- 在谷歌中搜索相关文章:USB的便携式ARINC429总线通信设备设计

- 在soso中搜索相关文章:USB的便携式ARINC429总线通信设备设计

- 在搜狗中搜索相关文章:USB的便携式ARINC429总线通信设备设计

当前位置:

当前位置: