AD6655在3G基站系统中的应用

[09-14 00:28:03] 来源:http://www.88dzw.com 通信电路 阅读:8847次

文章摘要:4 信号链的系统仿真 ADC采样后,153.6 MHz中频频点的三载波信号数字化为中心频点在30.72 MHz的信号。由于是实信号,因此在负频率处有其镜像信号。低中频信号进入数字混频器,转换为多载波0中频信号,同时将实数数据转换为In-phase和Quadrature正交的两部分分量。 AD6655的第一级滤波器为19阶的半带滤波器,它实现2倍抽取滤波,并且不能被旁路,因此它的带宽也决定了接收链路的最大带宽。器件手册指出最大可用带宽为采样率的11%,在122.88 MSPS采样率下支持的带宽为27 MHz。AD6655还有一个66阶的FIR滤波器,为抵消CIC滤波器对有用信号高频抑

AD6655在3G基站系统中的应用,标签:电路设计,http://www.88dzw.com4 信号链的系统仿真

ADC采样后,153.6 MHz中频频点的三载波信号数字化为中心频点在30.72 MHz的信号。由于是实信号,因此在负频率处有其镜像信号。

低中频信号进入数字混频器,转换为多载波0中频信号,同时将实数数据转换为In-phase和Quadrature正交的两部分分量。

AD6655的第一级滤波器为19阶的半带滤波器,它实现2倍抽取滤波,并且不能被旁路,因此它的带宽也决定了接收链路的最大带宽。器件手册指出最大可用带宽为采样率的11%,在122.88 MSPS采样率下支持的带宽为27 MHz。AD6655还有一个66阶的FIR滤波器,为抵消CIC滤波器对有用信号高频抑制的影响,FIR中加入了Inverse Sinc函数对高频信号进行补偿。

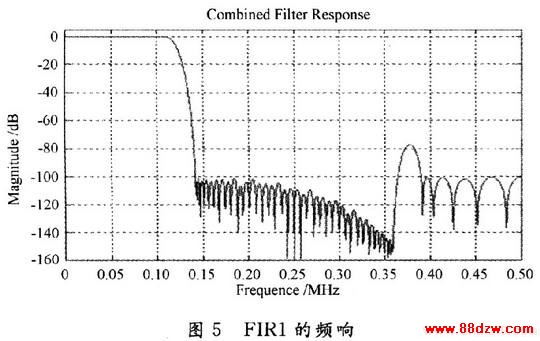

2级滤波器的级联频响如图5所示。

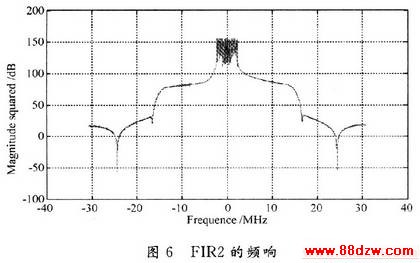

经过2级滤波器,AD6655输出信号的频谱特性如图6所示。

FPGA接收到AD6655的信号,由于已经对信号进行了2倍、或4倍的抽取,所以FPGA的工作频率就可以降低到ADC采样频率的了1/2或者1/4了。这对FPGA的型号选择和降低成本都是有利的。

FPGA需要继续对信号进行滤波和抽取,以达到系统ACS和Blocking要求的带外抑制度。由于AD6655可以对数字远端进行-80 dBc的抑制,那么FPGA只需要对带宽近端进行相应的滤波,通常90阶滤波器可以实现-50 dBc的带外抑制,当然采用分级滤波的方式效果可能更明显,并且一些滤波要在载波分路后进行。

FPGA需要继续对信号进行滤波和抽取,以达到系统要求的ACS和Blocking带外抑制度。由于AD6655可以对数字远端进行-80 dBc的抑制,那么FPGA只需要对带宽近端进行相应的滤波,通常90阶滤波器可以实现-50 dBc的带外抑制,当然采用分级滤波的方式效果可能更明显,并且一些滤波要在载波分路后进行。

5 仿真结果和评价

由以上仿真来看,AD6655可以满足基站上行链路中的应用,信号处理后输出给FPGA,节省了很多FPGA的逻辑单元。在AD6655Demo板和TD-SCDMA数字中频板卡DIFB 3.O进行了实测,测试结果完全符合设计要求。总之,AD6655是一款比较合适的数字中频接收链路的器件,可以应用在3G基站系统中,具有较高的性价比。

Tag:通信电路,电路设计,家电维修 - 单元电路介绍 - 通信电路

《AD6655在3G基站系统中的应用》相关文章

- › AD6655在3G基站系统中的应用

- 在百度中搜索相关文章:AD6655在3G基站系统中的应用

- 在谷歌中搜索相关文章:AD6655在3G基站系统中的应用

- 在soso中搜索相关文章:AD6655在3G基站系统中的应用

- 在搜狗中搜索相关文章:AD6655在3G基站系统中的应用

最新更新

当前位置:

当前位置: