基于FPGA和单片机的串行通信接口设计

[09-12 18:30:55] 来源:http://www.88dzw.com EDA/PLD 阅读:8755次

文章摘要: end if; when odd2=> --奇校验位 if ddb='1' then sout1<='0';state<=stop2; else sout1<='1';state<=stop2; end if; when stop2=> sout1<='1'; --

基于FPGA和单片机的串行通信接口设计,标签:eda技术,eda技术实用教程,http://www.88dzw.comend if;

when odd2=> --奇校验位

if ddb='1' then

sout1<='0';state<=stop2;

else

sout1<='1';state<=stop2;

end if;

when stop2=>

sout1<='1'; --停止位

if len="0000000000000000" then

state<=stop2;

else

state<=start1;

len<=len-1;

end if;

end case;

end if;

end process;

sout<=sout1;

end behav;

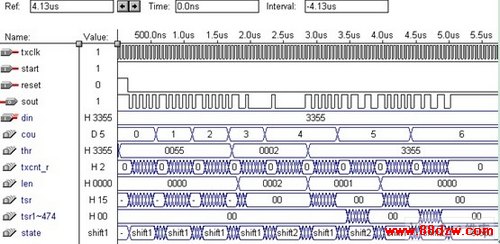

其中各信号的说明已在程序中标明了。波形仿真图如图2所示。

图2 FPGA数据发送时序仿真图

图中Din写入值为3355H,波特率为2400Hz,Start信号始终置逻辑1,即随时都能发送数据。Reset信号逻辑1时复位,逻辑0时电路开始工作。THR是数据寄存器,文件头、数据长度以及数据位都先寄存到THR中,Len是数据长度,TSR是低8位数据帧寄存器,TSR1是高8位数据帧寄存器。数据长度Len定为02H,发送时先发送低8位55H,后发送高8位33H,一共发送两遍。发送的数据格式说明:当发送55H时,其二进制为01010101,则发送的数据的二进制数为00101010111(1位开始位+8位数据位+1位奇校验位+1位停止位)。

单片机部分先对FPGA发送过来的文件头进行确认,正确就接收文件,否则放弃接收的数据。根据FPGA发送模块的协议,对串口控制寄存器SCON和波特率控制寄存器PCON的设置即可实现。

3 总结

目前电子产品的开发中经常要综合运用EDA技术、计算机控制技术、数字信号处理技术,那么电路各部分经常需要数据交换。本文也是基于此给出这方面应用的实例,供开发者交流。(作者:杜晓斌 陈兴文)

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

- 上一篇:VHDL设计的串口通信程序

《基于FPGA和单片机的串行通信接口设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA和单片机的串行通信接口设计

- 在谷歌中搜索相关文章:基于FPGA和单片机的串行通信接口设计

- 在soso中搜索相关文章:基于FPGA和单片机的串行通信接口设计

- 在搜狗中搜索相关文章:基于FPGA和单片机的串行通信接口设计

分类导航

最新更新

当前位置:

当前位置: