基于模块化设计方法实现FPGA动态部分重构

[09-12 18:33:57] 来源:http://www.88dzw.com EDA/PLD 阅读:8997次

文章摘要: 摘要:介绍了Xilinx FPGA的配置原理和FPGA模块化设计流程以及划分重构模块的原则。通过一个实例介绍了采用模块化设计方法实现Virtex-E FPGA动态部分重构的过程,能使重构模块在系统运行时改变其逻辑功能,而固定模块逻辑功能不中断,同时器件的重构时间大大减少。随着可编程技术的不断发展,FPGA被广泛应用于电子设计的各个领域。新的设计思想和设计方法也被不断的提出和应用,如FPGA的动态部分重构技术。所谓动态重构是指对于时序变化的数字逻辑系统,其时序逻辑的发生,不是通过调用芯片内不同区域不同逻辑资源的组合来实现,而是通过对具有专门缓存逻辑资源的FPGA,进行局部和全局芯片逻辑

基于模块化设计方法实现FPGA动态部分重构,标签:eda技术,eda技术实用教程,http://www.88dzw.com摘要:介绍了Xilinx FPGA的配置原理和FPGA模块化设计流程以及划分重构模块的原则。通过一个实例介绍了采用模块化设计方法实现Virtex-E FPGA动态部分重构的过程,能使重构模块在系统运行时改变其逻辑功能,而固定模块逻辑功能不中断,同时器件的重构时间大大减少。

随着可编程技术的不断发展,FPGA被广泛应用于电子设计的各个领域。新的设计思想和设计方法也被不断的提出和应用,如FPGA的动态部分重构技术。所谓动态重构是指对于时序变化的数字逻辑系统,其时序逻辑的发生,不是通过调用芯片内不同区域不同逻辑资源的组合来实现,而是通过对具有专门缓存逻辑资源的FPGA,进行局部和全局芯片逻辑的动态重构而快速实现。动态可重构FPGA器件在编程结构上应具有专门的特征,其内部逻辑块和内连线的改变可以通过读取不同的配置比特流文件来实现逻辑重建。动态部分重构是指重新配置FPGA的部分区域,重构过程中,FPGA其余部分的工作状态不受影响。此方式减小了重构范围和单元数目,从而大大缩短了FPGA的重构时间。

应用FPGA动态部分重构功能使硬件设计更加灵活,可用于硬件的远程升级、系统容错和演化硬件以及通信平台设计[1]等。动态部分重构可以通过两种方法实现:基于模块化设计方法(Module-Based Partial RecONfiguration)和基于差别的设计方法(Difference-Based Partial Reconfiguration),本文以基于模块化设计为例说明实现部分重构的方法。

1 FPGA配置原理简介

本文针对Xilinx公司的FPGA进行研究,支持模块化动态部分重构的器件族有Virtex/-II/-E和Virtex-II Pro。

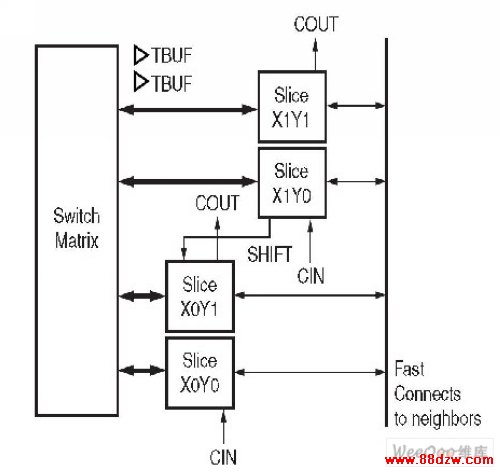

Xilinx公司FPGA是基于SRAM工艺的,包括配置逻辑块(CLBs),输入输出块(IOBs),块RAMs,时钟资源和编程布线等资源[2]。CLBs是构造用户所需逻辑的功能单元,IOBs提供封装引腿与内部信号引线的接口。可编程互连资源提供布线通道连接可配置元件的输入和输出到相应的网络。

存储在内部配置存储器单元中的数值决定了FPGA实现的逻辑功能和互接方式。Virtex FPGA的配置存储器是由配置列(Configuration ColumNS)组成的,这些配置列以垂直阵列的方式排列,如图1给出了Virtex-E XCV600E器件的配置列构成图。配置存储器可分为五种配置列:Center 列包含四个全局时钟的配置信息;两个IOB 列存储位于器件左边和右边所有IOBs的配置信息;CLB列存储FPGA基本逻辑功能的配置信息;Block SelectRAM Content列存储内部块RAM的配置信息;Block SelectRAM Interconnect列存储内部块RAM间互联的配置信息[3]。

图1 Virtex-E XCV600E的配置列构成及地址

配置列根据分配给它的配置地址(Configuration Address)来寻址。每一个配置列在FPGA内都有唯一的主地址(Major Address)空间。

FPGA的逻辑功能通过配置比特流(Configuration BitSTream)来实现。对于动态部分重构功能来说,需重构的配置逻辑是通过下载不同的部分配置比特流来实现的。

2基于模块化动态部分重构FPGA的设计方法

所谓的FPGA模块化设计就是将系统按照一定规则划分成若干模块,然后对每个模块分别进行设计、综合,并将实现结果约束在预先设置好的区域内,最后将所有模块的实现结果有机的组织起来完成整个系统的设计[4]。其划分模块的基本原则为:子模块功能相对独立,模块内部联系尽量紧密,模块间的连接尽量简单。对于那些难以满足模块划分准则的具有强内部关联的设计,不适合采用此设计方法。

FPGA模块化设计的优点在于:团队式并行工作从而加速整个项目的开发进度;每个子模块都能够灵活使用综合和实现工具独立进行优化,从而达到更好的优化结果;调试、更改某个子模块时,不会影响其他模块的实现结果,保证了整个设计的稳定性与可靠性。

模块化设计方法使用Xilinx公司的ISE软件设计工具,常用HDL语言作为设计输入,顶层模块描述设计的全局逻辑,包括设计的输入/输出、所有子模块的黑盒子(Black Box)声明以及子模块之间的连接关系。所谓黑盒子声明是指在顶层模块中仅仅对子模块进行端口描述与信号属性声明,并不包含任何实际逻辑和时序关系的描述。子模块通常也使用HDL语言描述,分别设计出各子模块的逻辑实体并综合所设计的子模块。由于子模块的输入/输出并不是整个设计的外部接口,所以在综合过程中应禁止子模块插入I/O端口,而仅在综合顶层模块时才插入I/O端口。最后将所有子模块的实现结果和顶层的实现结果有机地组织起立,完成整个设计的实现。图2是基于模块化设计方法的流程。

《基于模块化设计方法实现FPGA动态部分重构》相关文章

- › 基于模块化设计方法实现FPGA动态部分重构

- 在百度中搜索相关文章:基于模块化设计方法实现FPGA动态部分重构

- 在谷歌中搜索相关文章:基于模块化设计方法实现FPGA动态部分重构

- 在soso中搜索相关文章:基于模块化设计方法实现FPGA动态部分重构

- 在搜狗中搜索相关文章:基于模块化设计方法实现FPGA动态部分重构

当前位置:

当前位置: