基于Spartan-3 FPGA的视频采集系统设计

[09-12 18:29:35] 来源:http://www.88dzw.com EDA/PLD 阅读:8808次

文章摘要:引言视频采集的主流实现方案有两种:一是基于ASIC,该方案一般采用意法、AMD等公司的专用视频处理芯片;二是基于DSP,主要采用TI、ADI等公司的DSP信号处理器。它们作为辅处理器,可在主CPU控制下进行视频信号的采集压缩。随着FPGA的发展,通过SOPC技术实现视频采集已成为一种易于开发、设计灵活的方案。而这主要得益于IP复用技术的发展。在FPGA上构建复杂嵌入式系统可利用既有的功能模块及其驱动程序。该方案具有更大的集成度和灵活性,因而必将成为电子设计发展的一大趋势。本文介绍了采用Xilinx公司的Spartan-3 FPGA实现通用视频采集系统的设计方案。该系统外接模拟PAL/NTAL制

基于Spartan-3 FPGA的视频采集系统设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com引言

视频采集的主流实现方案有两种:一是基于ASIC,该方案一般采用意法、AMD等公司的专用视频处理芯片;二是基于DSP,主要采用TI、ADI等公司的DSP信号处理器。它们作为辅处理器,可在主CPU控制下进行视频信号的采集压缩。随着FPGA的发展,通过SOPC技术实现视频采集已成为一种易于开发、设计灵活的方案。而这主要得益于IP复用技术的发展。在FPGA上构建复杂嵌入式系统可利用既有的功能模块及其驱动程序。该方案具有更大的集成度和灵活性,因而必将成为电子设计发展的一大趋势。

本文介绍了采用Xilinx公司的Spartan-3 FPGA实现通用视频采集系统的设计方案。该系统外接模拟PAL/NTAL制式的摄像头,就能实时采集视频信号并进行MPEG-4格式压缩编码,码流可通过USB接口传给PC机,或通过以太网接口进行网络传输。本系统选用的是Spartan-3 FPGA系列的XC3S200芯片,该芯片有4320个逻辑单元(LC)、216Kbit BlockRAM、4个数字延迟锁相环(DDL)、173个用户I/O,而且逻辑密度高、I/O多、成本低。本设计主要涉及电路板级硬件设计、FPGA片级硬件系统设计和系统软件设计。

1 板级硬件设计

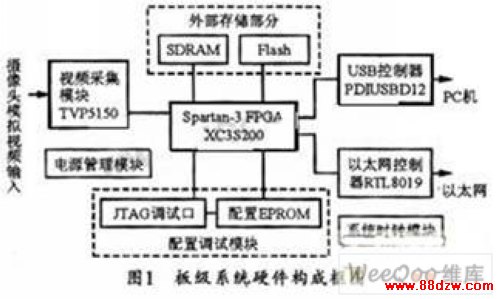

FPGA在电源和配置电路的支持下,即可构成嵌入式系统的最小化系统,并能实现片内的所有功能。在此最小化系统上,就可以根据本设计的应用需求,来扩展外部存储模块、视频采集模块、USB接口模块、以太网接口模块等功能模块电路,从而形成电路板级硬件平台。该板级硬件平台的结构组成如图1所示。

1.1 最小化系统

该FPGA是基于SRAM存储结构的器件。每次上电时可将配置数据从外部配置存储器加载到内部SRAM中,以使其构建逻辑结构从而实现逻辑功能。配置调试模块主要包括配置存储器、配置模式跳线开关和JTAG调试端口,其中JTAG调试端口是系统开发阶段PC机与FPGA的通信接口,可用于从PC机下载FPGA配置数据,并在程序调试阶段作为联机接口。本设计采用Xilinx公司Platform. Flash系列配置存储器XCF02S,并采用14针JTAG接口。模式跳线开关可决定FPGA是由JTAG还是由配置存储器来进行配置。系统时钟模块可对XC3S200提供50 MHz高频时钟信号,它采用高稳定性的石英晶体振荡器分立元件。电源管理模块采用DC/DC变换器来为系统各元件提供需要的各种电压电流。以上部分与FPGA芯片相连即可构成嵌入式系统工作的最小化系统。

1.2 外部存储扩展

由于XC3S200的片内存储容量有限且掉电即失,因此必须配置大容量的外部储存器。本设计扩展了4MByte的flash和32MByte的SDRAM (包括一片AMD公司的AM29LV320DT90EC型Flash和两片HYNIX公司的HY57V281620HCT-PI型SDRAM)。其中Flash在系统中用于存放程序代码、常量表以及一些在系统掉电后需要保存的用户数据。而SDRAM掉电数据即失,但其存取速度大大高于Flash且可读可写,因而在系统中用作程序的运行空间、临时数据及堆栈区等。

1.3 视频采集模块

TVP5150是TI公司推出的一款超低功耗的高性能混合信号视频解码芯片,可自动识别NTSC/PAL/SECAM制式的模拟信号,并将其按照YCbCr4:2:2的格式转化成数字信号,然后以8位内嵌同步信号的ITU-RBT.656格式输出。TVP5150具有价格低、体积小、操作简便等特点。FPGA对TVP5150芯片的操作是通过I2C总线实现的,数据传输连接方式采用最简单的ITU-RBT.656方式。

1.4 USB接口模块

USB接口模块选用PHILIPS公司的高性能USB接口芯片PDIUSBD12。该芯片完全符合USB1.1规范,可支持DMA传输,并可通过高速8位并行接口和FPGA进行通信,其最高并行接口速率可达到2 MB/s。

1.5 以太网接口模块

该模块采用Realtek公司生产的高度集成的以太网控制器RTL8019AS。RTL8019AS支持IEEE802.3标准和8位或16位数据总线。其内置16KB的SRAM可用于收发缓冲。在全双工模式时,其收发可同时达到10Mbps。RTL8019AS可支持10Base5、10Base2、10BaseT,并能自动检测所连接的介质。本设计采用RTL8019AS跳线接口模式,并通过16位数据总线连接FPGA。

《基于Spartan-3 FPGA的视频采集系统设计》相关文章

- › 基于Spartan-3 FPGA的视频采集系统设计

- › 基于SPCE061A的语音识别技术应用

- › Sunplus基于SPMC75的LIN结点方案

- › 基于SPMC75系列单片机的高性能三相变频电源

- 在百度中搜索相关文章:基于Spartan-3 FPGA的视频采集系统设计

- 在谷歌中搜索相关文章:基于Spartan-3 FPGA的视频采集系统设计

- 在soso中搜索相关文章:基于Spartan-3 FPGA的视频采集系统设计

- 在搜狗中搜索相关文章:基于Spartan-3 FPGA的视频采集系统设计

当前位置:

当前位置: