基于Spartan-3 FPGA的视频采集系统设计

[09-12 18:29:35] 来源:http://www.88dzw.com EDA/PLD 阅读:8808次

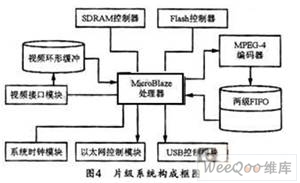

文章摘要:本系统的片内外设与MircoBlaze处理器的连接如图4所示,其中箭头表示视频数据的流向。3 系统软件设计系统中的MicroBlaze处理器对TVP515 0和PDIUSBD12的控制驱动程序可根据其通用驱动程序在EDK软件平台上移植生成。利用Xilinx公司提供的IP核可以搭建FPGA片内硬件平台,同时可获得底层硬件驱动程序的支持,然后在此基础上进行系统应用程序的开发。外部模拟视频信号经TVP5150转换为数字视频信号后,即可进入FPGA并通过视频接口模块直接排列到内部环形缓冲区数据队列的队尾。当MircoBlaze处理器接收到MPEG-4编码器可用中断时,系统将检测环形缓冲区是否为空。非空

基于Spartan-3 FPGA的视频采集系统设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com 本系统的片内外设与MircoBlaze处理器的连接如图4所示,其中箭头表示视频数据的流向。

3 系统软件设计

系统中的MicroBlaze处理器对TVP515 0和PDIUSBD12的控制驱动程序可根据其通用驱动程序在EDK软件平台上移植生成。利用Xilinx公司提供的IP核可以搭建FPGA片内硬件平台,同时可获得底层硬件驱动程序的支持,然后在此基础上进行系统应用程序的开发。

外部模拟视频信号经TVP5150转换为数字视频信号后,即可进入FPGA并通过视频接口模块直接排列到内部环形缓冲区数据队列的队尾。

当MircoBlaze处理器接收到MPEG-4编码器可用中断时,系统将检测环形缓冲区是否为空。非空时,可将数据队列的头部数据取出送给MPEG-4编码器,同时启动编码器编码。

视频信号经过编码器编成视频原码流后,即可进入FPGA内部二级FIFO缓存。当FIFO先一级满时向MircoBlaze处理器发出数据输出中断请求。

MircoBlaze处理器响应来自FIFO的中断后,可将FIFO先一级数据取出并以USB或以太网接口输出,然后清空FIFO先一级。

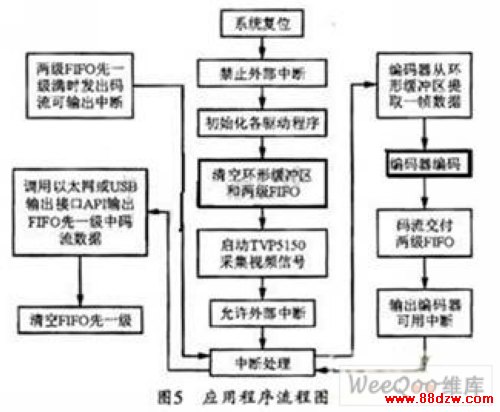

依据上面的工作过程,MircoBlaze处理器的应用程序包括以下几部分:

(1)系统复位初始化

即禁止外部中断,初始化各驱动程序,清空环形缓冲区和两级FIFO,检测USB接口、以太网接口连接以决定用何种方式输出,然后启动对TVP5150的控制并进行数据采集,最后启用外部中断。

(2)编码器可用中断服务

编码器完成一帧数据编码即可向MircoBlaze处理器发出中断,然后由MircoBlaze处理器控制编码器向环形缓冲区提取数据,并在环形缓冲区耗尽时等待一定时间;

(3)码流可输出中断服务

当两级FIFO先一级所准备输出的码流满时,可向MircoBlaze处理器发出中断,然后在MircoBlaze处理器控制下,将该码流交付给USB或以太网输出接口API并由底层驱动输出,最后再清空FIFO先一级。

图5所示是其应用程序流程图。

4 结束语

本设计介绍了基于Spartan-3 FPGA实现通用视频采集系统的实现方案。本系统的设计依赖于专用的设计软件和IP模块。由于采用了SOPC技术,该系统可裁减、可扩充、可升级,而多层次IP模块的高度复用又使得本系统具有设计周期短,风险投资小和设计成本低等优势。

《基于Spartan-3 FPGA的视频采集系统设计》相关文章

- › 基于Spartan-3 FPGA的视频采集系统设计

- › 基于SPCE061A的语音识别技术应用

- › Sunplus基于SPMC75的LIN结点方案

- › 基于SPMC75系列单片机的高性能三相变频电源

- 在百度中搜索相关文章:基于Spartan-3 FPGA的视频采集系统设计

- 在谷歌中搜索相关文章:基于Spartan-3 FPGA的视频采集系统设计

- 在soso中搜索相关文章:基于Spartan-3 FPGA的视频采集系统设计

- 在搜狗中搜索相关文章:基于Spartan-3 FPGA的视频采集系统设计

当前位置:

当前位置: