基于VerilogHDL的背景噪声扣除电路设计

[09-12 18:29:00] 来源:http://www.88dzw.com EDA/PLD 阅读:8679次

文章摘要:摘要:本文介绍了一种基于硬件描述语言VerilogHDL的背景噪声扣除电路设计,该设计与以往使用加减计数芯片组成的电路相比,具有与MCU接口简单,软件操作方便等优点。1 引言在微弱信号检测方法中,常需要使直流量经光电调制后转变为交流信号进行测量,以扣除背景噪声来提高系统信噪比。星载紫外遥感仪器同样采用了压频转换和调制解调实时扣除背景噪声、零点飘移的方案,但其原有实现背景噪声扣除功能的单元在与MCU接口及软件控制上稍显繁琐,而且布线面积较大。如能将背景噪声扣除功能设计成为具有通用接口和易操作的专用集成电路,对该仪器的升级换代有积极的意义。硬件描述语言VerilogHDL 提供了是一种在广泛的抽象

基于VerilogHDL的背景噪声扣除电路设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com摘要:本文介绍了一种基于硬件描述语言VerilogHDL的背景噪声扣除电路设计,该设计与以往使用加减计数芯片组成的电路相比,具有与MCU接口简单,软件操作方便等优点。

1 引言

在微弱信号检测方法中,常需要使直流量经光电调制后转变为交流信号进行测量,以扣除背景噪声来提高系统信噪比。星载紫外遥感仪器同样采用了压频转换和调制解调实时扣除背景噪声、零点飘移的方案,但其原有实现背景噪声扣除功能的单元在与MCU接口及软件控制上稍显繁琐,而且布线面积较大。如能将背景噪声扣除功能设计成为具有通用接口和易操作的专用集成电路,对该仪器的升级换代有积极的意义。

硬件描述语言VerilogHDL 提供了是一种在广泛的抽象层次上描述数字系统的方式,以其C语言风格,容易掌握等特点赢得了众多硬件设计师的青睐。通过软件编程来实现硬件功能后,下载到FPGA或CPLD大规模可编程逻辑器件,能将电路板级产品集成为芯片级产品。

为此,本文使用VerilogHDL进行编程,采用自顶向下的设计方法,经仿真验证和综合后,得到了具有通用接口和软件易于操作的背景噪声电路,弥补了原有单元的不足,取得了较好结果。

2 背景噪声扣除电路原理

紫外光谱遥感仪器电控部分由斩光器,精密高压电源及光电倍增管,单片机控制单元,同步累加解调单元,前置低噪声放大器,压频转换组成。其中斩光器将空间辐射光斩切成为交替的“信号+背景”和“背景”的光信号,使得光电倍增管输出的信号如图1所示。调制后的信号放大后,经压频转化后变为频率信号,通过同步累加单元的处理。同步累加解调单元采用四片四位二进制加减计数器SN54HC193进位位相连组成16位加减计数器,并配以逻辑门电路组成实现的。背景噪声的扣除功能是依靠16位加减计数器由时序控制,在通光状态下加计数,在遮光状态下减计数,经多周期计数实现。

图1经斩光器调制后由光电倍增管输出的信号

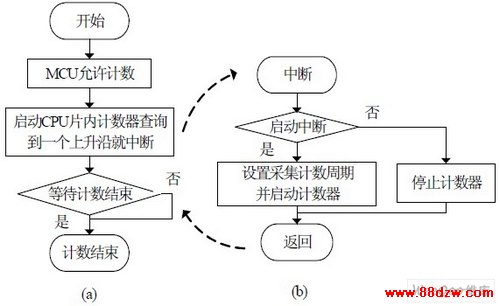

背景噪声扣除原理简单,但时序控制较繁琐。原有电路因布线面积和硬件芯片不易过多等诸多考虑,计数周期及启停控制采用软件两次中断设置来实现。如图2所示第一次为中断本文课题来源于国家自然科学基金资助项目项目批准号:60538020为启动计数,查询到斩光器信号第一个上升沿时进入,设置好计数周期后再次启动MCU片内计数器,以保证准确的查询到第一个上升沿时启动计数器。第二次为停止中断,采集计数周期溢出后停止计数。

图2 软件控制采集计数启停流程图

(a) MCU查询计数完成流程图 (b)中断执行计数器的启停控制流程图

易见原背景噪声扣除功能单元需要与MCU接口的数据线较多,需16条,且因不同微处理器片内资源不同,软件操作可能会更繁琐,可移植性不强。

综上,如果将背景噪声扣除功能单元设计成一个8位数据总线接口,高低字节分时复用,能对16位二进制数预置数和计数周期进行设置,操作上仅由MCU给出启动信号后,等查询完成信号便可读取计数结果的电路,则可大大减少线路板面积,使接口更简单,提高可操作性和移植性。

3 背景噪声扣除电路的VerilgHDL设计

依据自顶向下设计思想和自底向上的实现方法,背景噪声扣除电路的可划分为主模块(backnoise_deduct),16位二进制加减计数模块(bit16addsub),采集控制模块(Ctrol),读写接口模块(Addselec)四个模块。

主模块负责调用其它三个模块,并将输入输出接口进行连接。16位二进制加减计数模块负责在信号脉冲到来时,对给定的预置数在调制周期的高电平时加计数,在低电平时减计数。采集控制模块负责当MCU给出允许计数命令后,自动查询调制频率的第一个上升沿启动计数,在计数周期达到后停止计数,完成计数后通知MCU。读写接口模块负责与MCU接口,接收储存计数周期(斩光器信号或调制信号的周期数)和16位的预置数,并将最后计数结果返回MCU。

《基于VerilogHDL的背景噪声扣除电路设计》相关文章

- › 基于Verilog HDL的UART模块设计与仿真

- › 基于VerilogHDL的背景噪声扣除电路设计

- 在百度中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

- 在谷歌中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

- 在soso中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

- 在搜狗中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

当前位置:

当前位置: