基于VerilogHDL的背景噪声扣除电路设计

[09-12 18:29:00] 来源:http://www.88dzw.com EDA/PLD 阅读:8679次

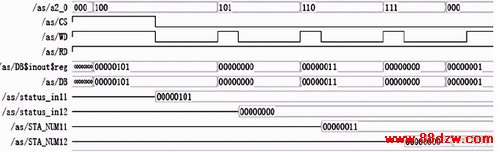

文章摘要:图4给出了使用ModelSim 软件对写信号有效的仿真波形,显示最后计数周期低、高8位写入的数值为00000101、00000000,预置数低、高8位数值为00000011、00000000。图4 计数周期和预置数在总线写入时的波形仿真结果4背景噪声扣除电路与MCU接口及软件操作图5背景噪声扣除电路的软件操作流程采用上述设计的集成背景噪声扣除电路在与MCU接口时十分方便。以MCS51系列单片机8051为例,最简单的连接方式为采用P1口与CLR、cpu_alw、stop_sign相连接,址线与CS、a2_0连接(可据电路规模设置片选方式),数据线、读写正常连接即可。软件操作不需要中断,操作流程

基于VerilogHDL的背景噪声扣除电路设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com 图4给出了使用ModelSim 软件对写信号有效的仿真波形,显示最后计数周期低、高8位写入的数值为00000101、00000000,预置数低、高8位数值为00000011、00000000。

图4 计数周期和预置数在总线写入时的波形仿真结果

4背景噪声扣除电路与MCU接口及软件操作

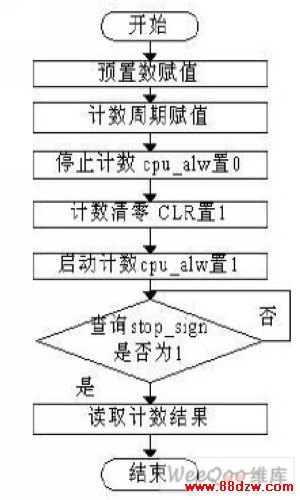

图5背景噪声扣除电路的软件操作流程

采用上述设计的集成背景噪声扣除电路在与MCU接口时十分方便。以MCS51系列单片机8051为例,最简单的连接方式为采用P1口与CLR、cpu_alw、stop_sign相连接,址线与CS、a2_0连接(可据电路规模设置片选方式),数据线、读写正常连接即可。软件操作不需要中断,操作流程如图5所示。更简单的做法是在系统初始化时将预置数和计数周期赋值为固定值即可。

5 结束语

本文介绍了采用计数器与门电路组成的背景噪声扣除电路的实现原理和工作方式,并分析了其局限性,然后提出了一种基于VerilogHDL 语言的背景噪声扣除电路的设计,使电路接口更为简单,软件更易操作,增强了移植性。该设计已经应用于在研的紫外遥感仪器中,为仪器的更新换代提供了技术支持。本文以通用性和简便性出发设计的背景噪声扣除电路的设计,将适用于以光电调制微弱直流量转换为交流信号测量的方案。

本文作者创新点:针对原有背景噪声扣除功能单元的局限性,用VerilogHDL语言设计出了接口方便、易操作的背景噪声扣除电路,使其有具备了较强的通用性和适用性。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《基于VerilogHDL的背景噪声扣除电路设计》相关文章

- › 基于Verilog HDL的UART模块设计与仿真

- › 基于VerilogHDL的背景噪声扣除电路设计

- 在百度中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

- 在谷歌中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

- 在soso中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

- 在搜狗中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

分类导航

最新更新

当前位置:

当前位置: