基于A/D和DSP的高速数据采集技术

[11-20 17:32:16] 来源:http://www.88dzw.com 模拟电子技术 阅读:8771次

文章摘要: 在中断中,DSP首先迅速关闭采样脉冲信号(使DX和FSX的输出为0),停止A/D转换器和F1FO的工作。TMS320C6713的CE0和ARE相“与”后与FIFO的读输入RCLK接在一起,DSP每执行一次I/O读操作,R=CE0十ARE便向RCLK发出一脉冲,把FIFO读使能PEN置为低,同时连续执行63次I/O读操作,数据便依次从IDT72V253送入TMS320C6713,整个数据采集工作就此完成。在进行第二次数据的采集前,最好将IDT72V253先复位,把TMS320C6713通用缓冲串口的CLKX配置为通用输出口,给IDT72V253的PRS引脚输入一个不小于10 ns的低脉冲

基于A/D和DSP的高速数据采集技术,标签:模拟电子技术基础,模拟电子电路,http://www.88dzw.com在中断中,DSP首先迅速关闭采样脉冲信号(使DX和FSX的输出为0),停止A/D转换器和F1FO的工作。TMS320C6713的CE0和ARE相“与”后与FIFO的读输入RCLK接在一起,DSP每执行一次I/O读操作,R=CE0十ARE便向RCLK发出一脉冲,把FIFO读使能PEN置为低,同时连续执行63次I/O读操作,数据便依次从IDT72V253送入TMS320C6713,整个数据采集工作就此完成。在进行第二次数据的采集前,最好将IDT72V253先复位,把TMS320C6713通用缓冲串口的CLKX配置为通用输出口,给IDT72V253的PRS引脚输入一个不小于10 ns的低脉冲,即在DSP的CLKX引脚输出一个低脉冲。这样可以更充分地保证FIFO的读、写指针的稳定。

3.3 软件设计

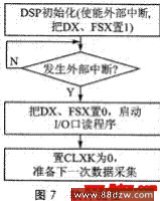

软件设计包括CPLD和DSP两个部分。CPLD程序用VHDL语言编写,实现简单的逻辑转换功能,程序设计比较简单。DSP编程中有几个关键步骤:外部中断使能、时钟送入A/D转换器和FIFO、等待中断、停止A/D转换器和FIFO、采集数据、复位FIFO。整个软件流程如图7所示。

4 结 论

通过实际设计表明,在DSP高速数据采集系统中,采用FIFO器件作为A/D转换器与DSP之间的桥梁,可以根据具体需要灵活设置FIFO的各个标志,使其具有很强的外部接口能力;并且通过软件很容易调整A/D转换器、FIFO和DSP的操作时序,增强了操作的灵活性,起到了很好的数据缓冲作用,保证了数据采集的安全可靠。系统硬件具有结构简单、性能可靠的特点;软件具有控制灵活、程序调试方便等优点。

Tag:模拟电子技术,模拟电子技术基础,模拟电子电路,模拟电子技术

《基于A/D和DSP的高速数据采集技术》相关文章

- › 基于AT0600的GPS接收机射频前端电路图

- › 基于AT0600的GPS接收机射频前端电路

- › ATR01610典型应用电路(基于ATR0610的GPS接收机低噪声放大电路)

- › 基于AHB接口的高性能LCD控制器IP设计

- › 基于ATmega128L的大容量MP3播放机

- › 基于ATmega128L与CC2420的无线传感器网络节点的研究与实现

- 在百度中搜索相关文章:基于A/D和DSP的高速数据采集技术

- 在谷歌中搜索相关文章:基于A/D和DSP的高速数据采集技术

- 在soso中搜索相关文章:基于A/D和DSP的高速数据采集技术

- 在搜狗中搜索相关文章:基于A/D和DSP的高速数据采集技术

分类导航

最新更新

当前位置:

当前位置: