针对高速串行接口设计的高效时钟解决方案

[09-13 16:53:51] 来源:http://www.88dzw.com 接口定义 阅读:8235次

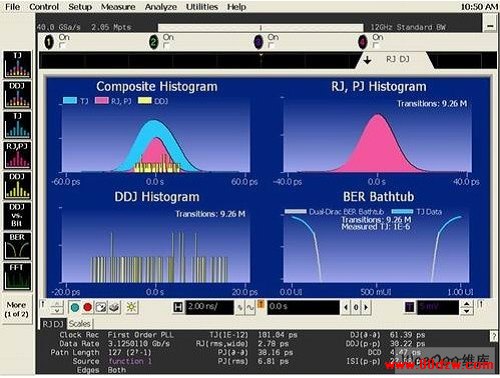

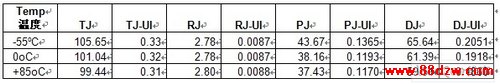

文章摘要:图4:抖动测试结果。表1ispClock 5406D的配置存储在片上非易失性存储器中,可通过JTAG接口进行再编程。器件上的许多功能还可以通过I2C接口进行“即时”修改。基于ispClock 5406D的系统的可编程特性支持许多附加功能,包括:TH和TCO时序裕度测量,有助于设计稳定性的测试;使用发送和接收通道间独立的偏移时钟的裕度测试,提高了可制造性;在数据有效窗口的中心进行准确的时钟对齐,增强了系统的可靠性。(作者:Srirama Chandra莱迪思半导体公司)上一页 [1] [2] [3]

针对高速串行接口设计的高效时钟解决方案,标签:接口技术,微机原理与接口技术,http://www.88dzw.com

图4:抖动测试结果。

表1

ispClock 5406D的配置存储在片上非易失性存储器中,可通过JTAG接口进行再编程。器件上的许多功能还可以通过I2C接口进行“即时”修改。基于ispClock 5406D的系统的可编程特性支持许多附加功能,包括:TH和TCO时序裕度测量,有助于设计稳定性的测试;使用发送和接收通道间独立的偏移时钟的裕度测试,提高了可制造性;在数据有效窗口的中心进行准确的时钟对齐,增强了系统的可靠性。(作者:Srirama Chandra

莱迪思半导体公司)

Tag:接口定义,接口技术,微机原理与接口技术,接口定义

《针对高速串行接口设计的高效时钟解决方案》相关文章

- › 针对高速串行接口设计的高效时钟解决方案

- 在百度中搜索相关文章:针对高速串行接口设计的高效时钟解决方案

- 在谷歌中搜索相关文章:针对高速串行接口设计的高效时钟解决方案

- 在soso中搜索相关文章:针对高速串行接口设计的高效时钟解决方案

- 在搜狗中搜索相关文章:针对高速串行接口设计的高效时钟解决方案

分类导航

最新更新

当前位置:

当前位置: