高速移动下OFDM均衡器的FPGA实现

[09-12 18:35:06] 来源:http://www.88dzw.com EDA/PLD 阅读:8500次

文章摘要:2.1.2 CIR模块介绍CIR模块完成矩阵迭代运算过程,它从输入端口读入Ak以及对应的,采用迭代的方法计算出,用FPGA实现这个模块的端口如图3所示。其中,CLK为时钟;γ是模拟信道的信噪比;Ak是频域转移矩阵G中取出的有效矩阵;trag是控制信号,当一次运算结束产生一个有效的后,只有trag被置为高电平才会进行下一次运算。取Q=2时,是一个5×5的矩阵。整个求逆矩阵的迭代过程就是从前一个5×5的逆矩阵(即)和从频域转移矩阵G中对应区域取得的5×9的矩阵Ak运算出下一个5×5逆矩阵(即)的过程。分析其矩阵求逆的迭代算法可以发现,其中大部分完成的是复数矩阵的乘加运算,所有数据是复数,虽然复杂很

高速移动下OFDM均衡器的FPGA实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com2.1.2 CIR模块介绍

CIR模块完成矩阵迭代运算过程,它从输入端口读入Ak以及对应的,采用迭代的方法计算出,用FPGA实现这个模块的端口如图3所示。

其中,CLK为时钟;γ是模拟信道的信噪比;Ak是频域转移矩阵G中取出的有效矩阵;trag是控制信号,当一次运算结束产生一个有效的 后,只有trag被置为高电平才会进行下一次运算。取Q=2时,

后,只有trag被置为高电平才会进行下一次运算。取Q=2时, 是一个5×5的矩阵。整个求逆矩阵的迭代过程就是从前一个5×5的逆矩阵(即

是一个5×5的矩阵。整个求逆矩阵的迭代过程就是从前一个5×5的逆矩阵(即 )和从频域转移矩阵G中对应区域取得的5×9的矩阵Ak运算出下一个5×5逆矩阵(即

)和从频域转移矩阵G中对应区域取得的5×9的矩阵Ak运算出下一个5×5逆矩阵(即 )的过程。

)的过程。

分析其矩阵求逆的迭代算法可以发现,其中大部分完成的是复数矩阵的乘加运算,所有数据是复数,虽然复杂很多,但是实际运算中有许多是多余的。Rk是共轭对称矩阵,上三角部分和下三角部分的实部相同,虚部也只是正负相反,所以只需要算出上三角矩阵的数据,下三角的部分直接对虚部取反就可以了。

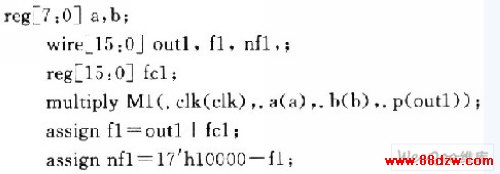

Xilinx的FPGA芯片中集成了硬核的乘加器DSP48,可以方便、高速地进行乘加运算。但是本算法中涉及到的复数运算比较灵活,还包括一些减法运算,直接使用DSP48不是很方便的控制。故设计了一种乘加器,使用了乘法器的IP Core,按照要求设置输入输出数据位数,其中的一个乘加运算中设置乘法器的两路输入为8位,输出为16位,调用IP Core如下所示,算法中其他的矩阵运算也都与此类似。

a,b作为两个寄存器储存参与运算的数据,outl是乘法器计算的结果,用fcl进行存放,相累加得到f1,再按照共轭复数运算的规律得到nfl。实现一个8位×8位的乘加器共消耗了56个Slice,32个LUT和49个IOB。该乘加器综合后的RTL结构图如图4所示。

为了能最大限度地提高运算速度,所有数据都用可编程逻辑单元构成的分布式存储器存储并列存储,并且根据算法的要求实现的是多个乘加器同时运算,这样虽然使用了很多逻辑资源,但任何数据都可以即取即用,便于进行大量的并行运算,以提高运算速度。

2.2 系统验证仿真

本系统采用Xilinx公司Virtex-2实验板进行仿真验证,该实验板采用的是XC2VP30芯片,它有30 816个逻辑单元,136个18位乘法器,2 448 KbRAM,资源丰富。开发软件为该公司的集成开发软件平台ISE 9.2,HDL语言采用Verilog,使用Matlab辅助ISE完成FPGA设计的方法。通过实验板上的RS 232串口与PC机进行通信,用Matlab从计算机中传输数据到FPGA芯片中,运算后再通过串口回传均衡后的信号数据到Matlab中仿真验证星座图,以判断该均衡器的效果。

2.2.1 均衡过程

CIR中使用迭代算法避免了并行大向量和大矩阵的运算,而是分步运算。所以对输入信号进行均衡,首先要进行并串变换,但是不需要变成真正的串行信号。当Q=2时,实际上对需要均衡的输入信号Y(i)每次取出5个数据,用yk表示,暂且将这样的变换叫作分组并串变换(P/GS),然后均衡矩阵ek与yk分组完成乘法运算得到一个zk,zk是一个数据不是向量,最后进行串并变换就得到均衡后的信号向量Z(i)。整个均衡的过程如图5所示。

《高速移动下OFDM均衡器的FPGA实现》相关文章

- › 高速移动下OFDM均衡器的FPGA实现

- 在百度中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

- 在谷歌中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

- 在soso中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

- 在搜狗中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

当前位置:

当前位置: