高速移动下OFDM均衡器的FPGA实现

[09-12 18:35:06] 来源:http://www.88dzw.com EDA/PLD 阅读:8500次

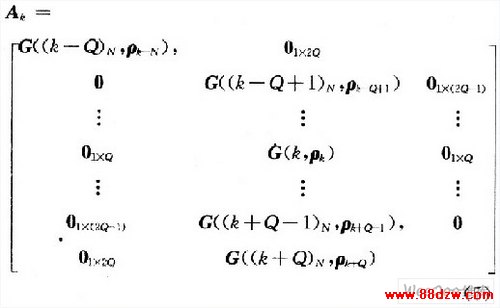

文章摘要:在时变信道中,G不是对角矩阵,则矩阵求逆的直接算法的运算量为o(N3),利用文献给出的结论:ICI主要来自相邻的几个子载波,并且每个子载波的符号能量主要泄漏至邻近的少数子载波上,也就是说,G中的很大一部分元素是可以忽略的。然后再采用迭代的方法对矩阵求逆,把运算量降为o(N2),但是在实际应用中,N是一个较大的数值,这个方法计算量仍然很大,所以很多算法在考虑均衡效果的同时也尽量减少运算量,以增强算法的可实现性和最终均衡的实时性。根据Chen等验证得到G可以被进一步简化成如下Ak来描述:式中:pn是一个由构成的1×(2Q+1)的矩阵,i=O,1,…,2Q。MMSE均衡器可以描述为;γ为该信道的信噪

高速移动下OFDM均衡器的FPGA实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com在时变信道中,G不是对角矩阵,则矩阵求逆的直接算法的运算量为o(N3),利用文献给出的结论:ICI主要来自相邻的几个子载波,并且每个子载波的符号能量主要泄漏至邻近的少数子载波上,也就是说,G中的很大一部分元素是可以忽略的。然后再采用迭代的方法对矩阵求逆,把运算量降为o(N2),但是在实际应用中,N是一个较大的数值,这个方法计算量仍然很大,所以很多算法在考虑均衡效果的同时也尽量减少运算量,以增强算法的可实现性和最终均衡的实时性。

根据Chen等验证得到G可以被进一步简化成如下Ak来描述:

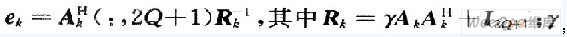

式中:pn是一个由 构成的1×(2Q+1)的矩阵,i=O,1,…,2Q。MMSE均衡器可以描述为;

构成的1×(2Q+1)的矩阵,i=O,1,…,2Q。MMSE均衡器可以描述为; γ为该信道的信噪比,且

γ为该信道的信噪比,且 。Ak是一个(2Q+1)×(4Q+1)的矩阵,再利用文献中迭代的方法来计算矩阵的逆。对于一个OFDM模块来说,该算法的总计算量是o((2Q+1)2N),由于Q<

。Ak是一个(2Q+1)×(4Q+1)的矩阵,再利用文献中迭代的方法来计算矩阵的逆。对于一个OFDM模块来说,该算法的总计算量是o((2Q+1)2N),由于Q<

当载波数比较大时,OFDM均衡算法所要计算的矩阵比较庞大,计算量大,很难保证实时性的要求。于是人们很自然地会想到用实时性很强的FPGA来实现均衡器的设计,但是均衡本身所需要处理的数据量和运算量都非常大,即使使用FPGA实现也很困难。

若采用文献中的算法运算量是o(N2),假如当载波数N=128时,运算量还是很大的,无法保证实时性。从均衡效果和运算量两方面考虑,采用了文献中的算法。这是一种典型的迭代算法,效果与文献算法相接近,但是在计算中避免了求一个很大的矩阵的逆运算,而是从频域转移矩阵G中提取出了不大的有效矩阵,这样就减少了大量运算。

2.1 硬件设计思想

在对均衡器算法进行FPGA设计之前,先用Matlab仿真该均衡器浮点算法,通过分析程序可以发现,该算法的核心部分是迭代求逆矩阵的过程。该算法的瓶颈主要是求解由复数元素组成的矩阵的逆的计算量巨大,而且是浮点数会占用很大的存储空间。为尽量减少需要使用的逻辑资源,在进行ISE设计时,数据用16位定点数表示,其中高8位是整数部分,低8位是小数部分。

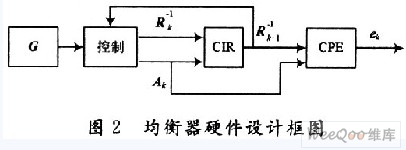

2.1.1 硬件设计框图

实现该均衡器的硬件设计框图如图2所示,其中G为从Matlab中产生的频域转移矩阵,控制模块完成从G中取出对应的有效值得到Ak,并且控制当一组运算完成后运用上一组产生的 。进行下一组运算,CIR是该算法的核心,即矩阵迭代求逆的运算,CPE模块是一个简单的矩阵运算模块完成

。进行下一组运算,CIR是该算法的核心,即矩阵迭代求逆的运算,CPE模块是一个简单的矩阵运算模块完成 的运算。

的运算。

《高速移动下OFDM均衡器的FPGA实现》相关文章

- › 高速移动下OFDM均衡器的FPGA实现

- 在百度中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

- 在谷歌中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

- 在soso中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

- 在搜狗中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

当前位置:

当前位置: