一种基于FPGA的自适应谱线增强系统的设计

[09-12 18:33:00] 来源:http://www.88dzw.com EDA/PLD 阅读:8175次

文章摘要:其中:ARRAY_N1BIF定义的是滤波器参数向量的数据类型;ARRAY_N1BIYX定义的延迟后信号向量的数据类型;ARRAY_N1BIT定义的是输入信号向量的数据类型;ARRAY_N2BIT定义的是谱线增强后信号向量的数据类型;W1是采样数据的宽度,这里为8;Delay是延时长度;L是滤波器阶数。3.3 LMS算法核心模块这是设计的核心部分也是设计中的难点。用FPGA实现复杂数字信号处理并不像DSP中那样简单,需要考虑时序同步、数据宽度以及如何舍入。该设计采用16阶自适应滤波器实现ALE,滤波器初始权值全部为0,按照式(3)的算法进行迭代更新,算法实现中用到大量乘法运算。调用芯片内部嵌入的

一种基于FPGA的自适应谱线增强系统的设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com其中:ARRAY_N1BIF定义的是滤波器参数向量的数据类型;ARRAY_N1BIYX定义的延迟后信号向量的数据类型;ARRAY_N1BIT定义的是输入信号向量的数据类型;ARRAY_N2BIT定义的是谱线增强后信号向量的数据类型;W1是采样数据的宽度,这里为8;Delay是延时长度;L是滤波器阶数。

3.3 LMS算法核心模块

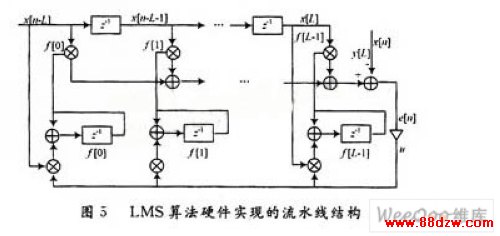

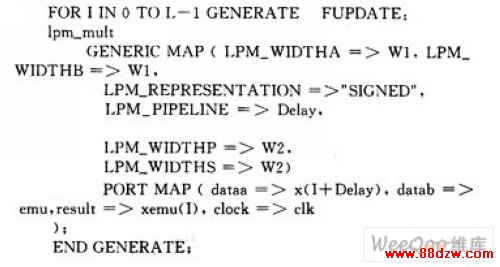

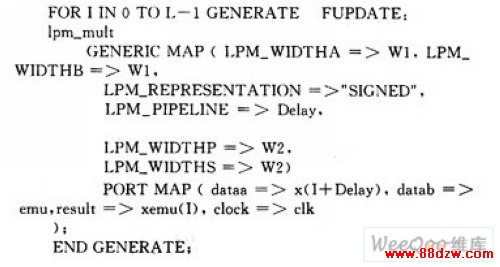

这是设计的核心部分也是设计中的难点。用FPGA实现复杂数字信号处理并不像DSP中那样简单,需要考虑时序同步、数据宽度以及如何舍入。该设计采用16阶自适应滤波器实现ALE,滤波器初始权值全部为0,按照式(3)的算法进行迭代更新,算法实现中用到大量乘法运算。调用芯片内部嵌入的乘法器宏功能模块lpm_mult使实现这些乘法运算更加快速、高效的方案。lpm_mult模块输入采样的8位数据,因为在乘法运算中2个8位二进制数相乘得到的结果是1个16位二进制数,所以设计中将处理结果输出为16位二进制数。为了提高自适应滤波速度,设计中采用流水线的滤波器结构。流水线结构能够显著地提高处理的速度,但是要消耗更多的硬件资源,特别是硬件乘法器,如果LMS FIR滤波器的长的为L则需要2L个通用乘法器。设计中L=16,片内有36个片内乘法器可以胜任处理要求。编译结果显示片内应用于LMS核心算法的其他资源消耗全部小于或等于总消耗的6%,其余资源可以用于片内的采样、输出等时序控制。LMS算法硬件实现的流水线结构框图如图5所示。

流水线结构中调用乘法器的VHDL代码如下:

4 仿真结果分析

VHDL程序在QuartusⅡ软件上部分仿真结果如图6所示,图中仿真数据以十进制表示。因为仿真结果不便于绘制类似Matlab中的图形,将仿真结果的数据与Matlab仿真结果进行对比。通过行比较,发现处理结果在大体上与Matlab相一致,但是在幅度上整体有些衰减,这是由于FPGA中将处理结果的低位进行截尾处理,而Matlab仿真环境使用浮点形式、数据位数长,处理精度远高于FPGA,FPGA设计中存在较大的截尾误差。该仿真结果表明,基于:FPGA实现ALE是切实可行的。

5 结 语

系统采用FPGA芯片加上少量的外围电路,完成了信号的自适应谱线增强。通过调用FPGA片内乘法器和片内存储器,完成了LMS算法的自适应谱线增强,仿真结果与理论相符合。现代数字信号处理算法大多要进行大量的乘法运算,调用FPGA片内乘法器是实现这些算法的快速高效而又经济的手段,这使得复杂信号处理算法在FPGA上实现成为可能。流水线结构是硬件设计中牺牲资源以提高速度的有效手段,有效地利用流水线可以显著地提高资源利用率和处理速度。该设计可以实现高速、准确地谱线增强,在需要滤除宽带噪声提取单根谱线的领域具有一定的现实意义。

《一种基于FPGA的自适应谱线增强系统的设计》相关文章

- › 一种基于Modelsim FLI接口的协同仿真技术

- › 一种基于S7-200 PLC的位置控制器研究设计

- › 一种基于CPLD的声发射信号传输系统设计

- › 一种基于FPGA的VGA图象信号发生器设计

- › 一种基于H.264的快速运动估计算法

- › 一种基于FPGA的多路视频通道控制系统设计

- 在百度中搜索相关文章:一种基于FPGA的自适应谱线增强系统的设计

- 在谷歌中搜索相关文章:一种基于FPGA的自适应谱线增强系统的设计

- 在soso中搜索相关文章:一种基于FPGA的自适应谱线增强系统的设计

- 在搜狗中搜索相关文章:一种基于FPGA的自适应谱线增强系统的设计

当前位置:

当前位置: