VHDL设计的微型打印机控制器技术

[09-12 18:31:22] 来源:http://www.88dzw.com EDA/PLD 阅读:8430次

文章摘要:1 引言VHDL是一种面向设计、多层次的数字系统设计的标准化硬件描述语言,VHDL不需依赖冯・诺伊曼结构,可实现时序和真正并行设计,从而开辟一种全新的数字系统的设计途径。使用VHDL语言更便于建立层次结构和元件结构设计。VHDL编写的电路模块代码可重复利用,故简化设计,缩短设计时间,提高工作效率。2 TP UP-SF微型打印机简介TP UP-SF系列的高速微型打印机,采用针式撞击点阵打印,是一类体积小、打印速度快的打印输出设备。该系列打印机配有串行和并行接口,实现汉字的高速打印,可装外径70 mm大打印纸卷。此系列打印机比较小巧,携带方便,适用于小型收款机、小型计费器、*终端等各种应用场合。T

VHDL设计的微型打印机控制器技术,标签:eda技术,eda技术实用教程,http://www.88dzw.com1 引言

VHDL是一种面向设计、多层次的数字系统设计的标准化硬件描述语言,VHDL不需依赖冯・诺伊曼结构,可实现时序和真正并行设计,从而开辟一种全新的数字系统的设计途径。使用VHDL语言更便于建立层次结构和元件结构设计。VHDL编写的电路模块代码可重复利用,故简化设计,缩短设计时间,提高工作效率。

2 TP UP-SF微型打印机简介

TP UP-SF系列的高速微型打印机,采用针式撞击点阵打印,是一类体积小、打印速度快的打印输出设备。该系列打印机配有串行和并行接口,实现汉字的高速打印,可装外径70 mm大打印纸卷。此系列打印机比较小巧,携带方便,适用于小型收款机、小型计费器、*终端等各种应用场合。

TP UP-SF支持EPSON M一180、M―190和M一160系列的10种机头打印;可配置的串行和并行接口,根据打印机型号不同,TP UP―SF的打印速度可达2.5行/s,打印密度最高为252点/行。

微型打印机具有40个通用ESC/P打印控制命令和FS汉字打印控制命令。其中包括:字符、点阵图形打印命令和汉字打印命令。对于前者ESC/P命令支持字符打印及放大,上、下划线和点正图形,用户自定义字符打印,实现打印格式设置,十六进制形式打印等功能。而后者,FS命令支持机内国标一、二级硬汉字库打印汉字,罗马字母(A6区)和制表符(A9区)。

3 微型打印机的接口连接

3.1 串口连接

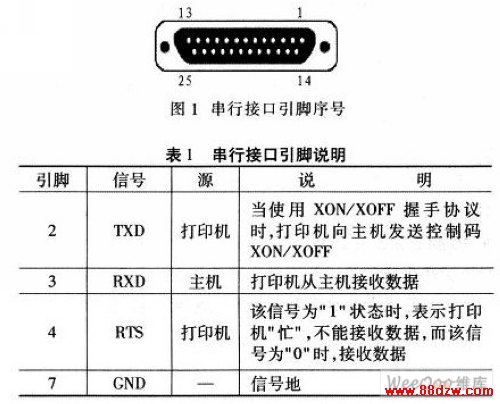

TP UP―SF系列打印机的S型机采用与RS-232C标准兼容的D一25串行接口,其接口插座则与IBM PC的RS一232C相配合。串行接口引脚排列如图l所示,表l为串行接口引脚信号说明。

有2种握手方式可供选用,一种是标志控制方式,另一种是XON/XOFF协议方式。串行数据传输采用异步通讯格式,串行通讯的数据格式和波特率可由用户自行设定。

3.2 并口连接

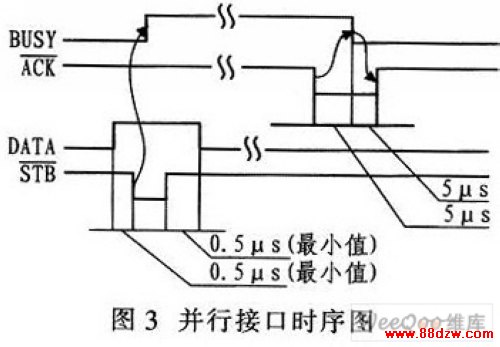

TP UP-SF系列打印机的P型机采用与Centmnics标准兼容的D一25并行接口,接口插座则与IBM PC的打印接口相配合。并行接口引脚排列如图2所示,表2为并行接口引脚信号说明。

图3为并行接口的时序,FPGA按照这些信号工作时序进行正确控制。当输入信号进入打印机时,即可驱动打印机完成打印工作。

4 系统设计

按照从上至下的可编程系统设计思想,利用Ahera公司的CYCL0N系列FPGA器件,通过QUARTUS II开发工具,完成了FPGA所需的硬件系统的设计和软件开发。采用模块式设计,从存储器读取数据,再送入至微型打印机打印。

4.1 硬件电路设计

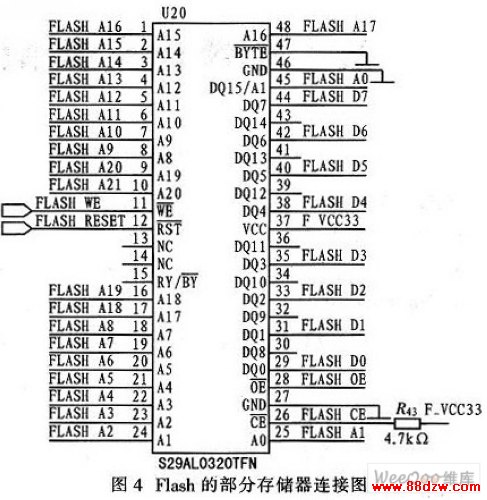

硬件电路以FPGA为中心,实现存储器的接口电路设计,以及对打印机的并口接口电路设计。该系统设计采用Flash存储器,它是一种可擦除、非易失性存储器,可实现数据的存储功能,便于数据传输。图4为Flash存储器的部分电路连接图。

4.2 基于状态机的打印控制模块设计

微型打印机控制模块主要控制打印机的工作时序,使其能够正常工作。控制模块主要是利用VHDL语言的状态机实现。根据时序图并结合打印机特性,在编写状态机时,分为3个状态,其状态转换图如图5所示。

《VHDL设计的微型打印机控制器技术》相关文章

- › 基于VHDL 的矩阵键盘及显示电路设计

- › 基于VHDL的可变速彩灯控制器的设计

- › VHDL语言为核心的EDA技术在医学中的应用

- › VHDL设计的微型打印机控制器技术

- › VHDL设计中信号与变量问题的研究

- › 基于VHDL的图像传感器TCDl206的驱动设计

- 在百度中搜索相关文章:VHDL设计的微型打印机控制器技术

- 在谷歌中搜索相关文章:VHDL设计的微型打印机控制器技术

- 在soso中搜索相关文章:VHDL设计的微型打印机控制器技术

- 在搜狗中搜索相关文章:VHDL设计的微型打印机控制器技术

当前位置:

当前位置: