FPGA设计的SPI自动发送模块技术

[09-12 18:30:48] 来源:http://www.88dzw.com EDA/PLD 阅读:8462次

文章摘要:end if;end if;end process;--24bit SPI 时钟采集生成模块counter24_u:process(LCD_SCLSS)beginif SPI_WR='1' thencounter24<="110011";elsif LCD_SCLSS='1' and LCD_SCLSS'event thenif counter24>0 thencounter24<=counter24-1;if (counter24="000000")or(counter24="0000

FPGA设计的SPI自动发送模块技术,标签:eda技术,eda技术实用教程,http://www.88dzw.comend if;

end if;

end process;

--24bit SPI 时钟采集生成模块

counter24_u:process(LCD_SCLSS)

begin

if SPI_WR='1' then

counter24<="110011";

elsif LCD_SCLSS='1' and LCD_SCLSS'event then

if counter24>0 then

counter24<=counter24-1;

if (counter24="000000")or(counter24="000001")or

(counter24="110011")or(counter24="000010")then

LCD_SCLSS24<='0';

else

LCD_SCLSS24<=LCD_SCLSSS;

end if;

end if;

end if;

end process;

--8bit 数据移位模块

DB8BIT_U:process(shift,SPI_WR,DBINOUTS)

begin

if SPI_WR='1' then

DB8BIT_reg<=DBINOUTS(7 downto 0);

else

if shift='1' and shift'event then

LCD_SDIS_8BIT<=DB8BIT_reg(0);

DB8BIT_reg(6 downto 0)<=DB8BIT_reg(7 downto 1);

end if;

end if;

end process;

--16bit 数据移位模块

DB16BIT_U:process(shift,SPI_WR,DBINOUTS)

begin

if SPI_WR='1' then

DB16BIT_reg(15 downto 0)<=DBINOUTS(15 downto 0);

else

if shift='1' and shift'event then

LCD_SDIS_16BIT<=DB16BIT_reg(0);

DB16BIT_reg(14 downto 0)<=DB16BIT_reg(15 downto 1);

end if;

end if;

end process;

--24bit 数据移位模块

DB24BIT_U:process(shift,SPI_WR,DBINOUTS)

begin

if SPI_WR='1' then

DB24BIT_reg(23 downto 0)<=DBINOUTS(23 downto 0);

else

if shift='1' and shift'event then

LCD_SDIS_24BIT<=DB24BIT_reg(0);

DB24BIT_reg(22 downto 0)<=DB24BIT_reg(23 downto 1);

end if;

end if;

end process;

end;

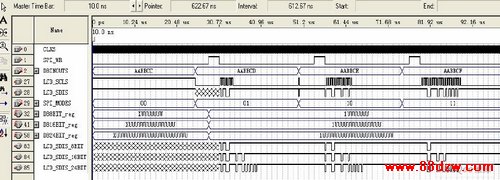

五、仿真波形图

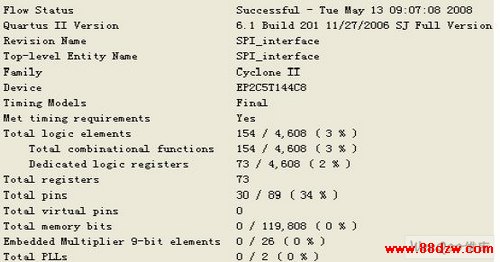

六、编译后资源占用情况

七、结束语

本文旨在给学习可编程技术的人们提供一个参考,起到抛砖引玉的作用。望阅读过此文的读者提供更好的方法,与所有的学习者共享,共勉!(作者:姚青华)

《FPGA设计的SPI自动发送模块技术》相关文章

- › 高性能FPGA中的高速SERDES接口

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › FPGA在平板显示器中的应用

- › FPGA与DS18B20型温度传感器通信的实现

- 在百度中搜索相关文章:FPGA设计的SPI自动发送模块技术

- 在谷歌中搜索相关文章:FPGA设计的SPI自动发送模块技术

- 在soso中搜索相关文章:FPGA设计的SPI自动发送模块技术

- 在搜狗中搜索相关文章:FPGA设计的SPI自动发送模块技术

当前位置:

当前位置: