FPGA设计的SPI自动发送模块技术

[09-12 18:30:48] 来源:http://www.88dzw.com EDA/PLD 阅读:8462次

文章摘要:一、摘要:SPI 接口应用十分广泛,在很多情况下,人们会用软件模拟的方法来产生SPI 时序或是采用带SPI 功能模块的MCU。但随着可编程逻辑技术的发展,人们往往需要自己设计简单的SPI 发送模块。本文介绍一种基于FPGA 的将并行数据以SPI 串行方式自动发送出去的方法。二、关键字:VHDL、FPGA、SPI、串行数据输出选择模块、移位脉冲产生模块、SPI 时钟采集信号和无相移的SPI 基准时钟产生模块、SPI 时钟输出选择模块、8bit SPI 时钟采集生成模块、16bit SPI 时钟采集生成模块、24bit SPI 时钟采集生成模块、8bit 数据移位模块、16bit 数据移位模块、2

FPGA设计的SPI自动发送模块技术,标签:eda技术,eda技术实用教程,http://www.88dzw.com一、摘要:

SPI 接口应用十分广泛,在很多情况下,人们会用软件模拟的方法来产生SPI 时序或是采用带SPI 功能模块的MCU。但随着可编程逻辑技术的发展,人们往往需要自己设计简单的SPI 发送模块。本文介绍一种基于FPGA 的将并行数据以SPI 串行方式自动发送出去的方法。

二、关键字:

VHDL、FPGA、SPI、串行数据输出选择模块、移位脉冲产生模块、SPI 时钟采集信号和无相移的SPI 基准时钟产生模块、SPI 时钟输出选择模块、8bit SPI 时钟采集生成模块、16bit SPI 时钟采集生成模块、24bit SPI 时钟采集生成模块、8bit 数据移位模块、16bit 数据移位模块、24bit 数据移位模块。

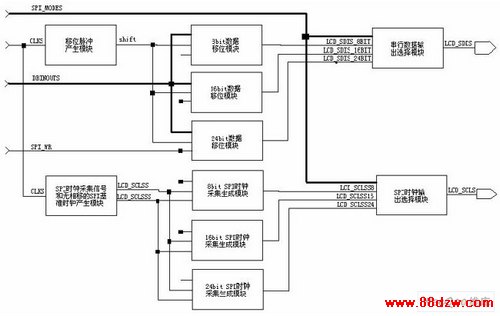

三、功能框图:

SPI_MODES 为输入模式选择端口:

--"01"is 8bit 传输模式

--"10"is 16bit 传输模式

--"11"is 24bit 传输模式

CLKS 为整个模块的基准时钟

DBINOUTS 为并行数据输入端口:

--8bit 模式为DBINOUTS(7 downto 0)

--16bit 模式为DBINOUTS(15 downto 0)

--24bit 模式为DBINOUTS(23 downto 0)

SPI_WR 为启动SPI 传输的信号

整个功能模块可工作在 8bit、16bit、24bit SPI 猝发传输状态。对其进行软件操作的步骤相当简单:

--此模块软件操作流程如下

--1、SPI_MODES="xx" 设定串口操作模式

--2、DBINOUTS="xxxxxxxxxxxxxxxxxxxxxxxx" 输入要发射的数据

--3、SPI_WR='0'

--4、SPI_WR='1'

--5、SPI_WR='0'

--8bit 模式延时2*8*4*CLKS

--16bit 模式延时2*1**CLKS

--24bit 模式延时2*24*4*CLKS

--6、DBINOUTS="xxxxxxxxxxxxxxxxxxxxxxxx" 输入下一个要发射的数据

四、VHDL 描述解读

--以下描述的是一个SPI 自动发射模块

--在很多情况下,人们会用软件模拟的方法来产生SPI 时序

--这里采用硬件的方法,即使软件操作更为简单,有提高了传输的速度

--------------------------------------------------------------

--此模块软件操作流程如下

--1、SPI_MODES="xx" 设定串口操作模式

--2、DBINOUTS="xxxxxxxxxxxxxxxxxxxxxxxx" 输入要发射的数据

--3、SPI_WR='0'

--4、SPI_WR='1'

--5、SPI_WR='0'

--8bit 模式延时2*8*4*CLKS

--16bit 模式延时2*1**CLKS

--24bit 模式延时2*24*4*CLKS

--6、DBINOUTS="xxxxxxxxxxxxxxxxxxxxxxxx" 输入下一个要发射的数据

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity SPI_interface is

port(CLKS :in std_logic; --基准时钟

LCD_SCLS :out std_logic;--SPI 发射时钟,上升沿有效

LCD_SDIS :out std_logic;--SPI 数据串行输出口

SPI_MODES :in std_logic_vector(1 downto 0);

--串口操作模式选择

--"01"is 8bit trans mode

--"10"is 16bit trans mode

--"11"is 24bit trans mode

SPI_WR :in std_logic; --启动串口发送信号

DBINOUTS :in std_logic_vector(23 downto 0));

--背发送数据的并行输入口

--8bit mode use DBINOUTS(7 downto 0)

--16bit mode use DBINOUTS(15 downto 0)

--24bit mode use DBINOUTS(23 downto 0)

end;

architecture SPI_interface_behav of SPI_interface is

signal DB8BIT_reg :std_logic_vector(7 downto 0); --8bit 数据移位寄存器

signal DB16BIT_reg :std_logic_vector(15 downto 0);--16bit 数据移位寄存器

《FPGA设计的SPI自动发送模块技术》相关文章

- › 高性能FPGA中的高速SERDES接口

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › FPGA在平板显示器中的应用

- › FPGA与DS18B20型温度传感器通信的实现

- 在百度中搜索相关文章:FPGA设计的SPI自动发送模块技术

- 在谷歌中搜索相关文章:FPGA设计的SPI自动发送模块技术

- 在soso中搜索相关文章:FPGA设计的SPI自动发送模块技术

- 在搜狗中搜索相关文章:FPGA设计的SPI自动发送模块技术

当前位置:

当前位置: