直扩导航系统中数字科思塔斯环的FPGA设计与实现

[09-12 18:29:06] 来源:http://www.88dzw.com EDA/PLD 阅读:8442次

文章摘要:低通滤波器数字低通滤波器实际上是由累加器和寄存器所组成的一个积分清洗器,它的作用是去掉数字混频器后的高次谐波。累加器对数字混频后输入信号与本地码相乘的每一位结果进行累加,经过一个码周期时间(本方案为15000次)的积分累积后,得到一个数据位的相关值。该积分清洗器的累加时钟为中频采样时钟,清洗脉冲是累加一个数据位的进位脉冲,并要求它的时钟沿跟其采样时钟保持一致,其FPGA实现顶层原理结构如图4所示。在FPGA中对积分清洗模块进行仿真,仿真中输入信号data为1,在某一时刻,使累加清洗信号aclr有效。下载到FPGA中利用SignalTap II对积分清洗模块进行测试,测试中输入数据为1,当累加到

直扩导航系统中数字科思塔斯环的FPGA设计与实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com

低通滤波器

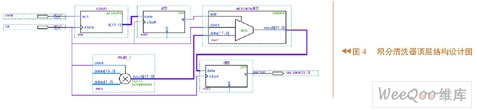

数字低通滤波器实际上是由累加器和寄存器所组成的一个积分清洗器,它的作用是去掉数字混频器后的高次谐波。累加器对数字混频后输入信号与本地码相乘的每一位结果进行累加,经过一个码周期时间(本方案为15000次)的积分累积后,得到一个数据位的相关值。该积分清洗器的累加时钟为中频采样时钟,清洗脉冲是累加一个数据位的进位脉冲,并要求它的时钟沿跟其采样时钟保持一致,其FPGA实现顶层原理结构如图4所示。

在FPGA中对积分清洗模块进行仿真,仿真中输入信号data为1,在某一时刻,使累加清洗信号aclr有效。下载到FPGA中利用SignalTap II对积分清洗模块进行测试,测试中输入数据为1,当累加到14时,使清洗信号有效。测试结果(图略)验证了设计的正确性。

数字鉴相器的设计

科斯塔斯环常用的鉴相器是正弦和反正切鉴相器。对于本文设计的接收机,积分时间T_{d}=0.25ms,4kHz的信号在0.25ms内将变化1周,二象限反正切算法的鉴相范围为[π/2,π/2],因此必须保证输入信号在0.25ms内变化不超过 ,即允许最大的频差为2kHz,否则将得到错误的输出。因此必须对鉴相器的输出进行校正。实际设计时通过计算前后两次鉴别器的输出差值,根据差值大小进行校正,校正算法为:当 ,就对取反,否则 保持不变,其中 为上一次鉴别器误差输出, 为本次鉴别器误差输出。

环路数字滤波器参数的设计

环路选用的是理想二阶环,带宽的大小又决定了整个锁相环的锁定时间和跟踪精度。为了减小噪声引起的相位抖动,提纯输入信号,环路带宽应尽量取窄一些,选取环路噪声带宽跟信息数据速率的比为,其中B_{L}为环路噪声等效带宽,R_{b}为信息数据速率,一般选取 ,另一方面,也要兼顾捕获时间,从而环路带宽又要求取宽一些,因此应折衷考虑设计的环路带宽。当环路处于频率牵引状态时,要求环路有较宽的捕捉频带,使之能迅速同步频偏较大的载波;当环路处于相位跟踪或锁定状态时,却要求它具有尽量窄的捕捉频带,以保证恢复出的载波相位不产生大的抖动。设计时应根据具体要求来选择环路参数。

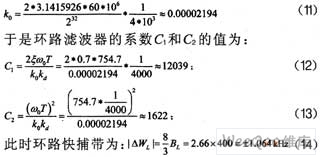

在本方案中,设计要求数据率为4kbps,在频率跟踪阶段,取B_{L}=0.1R_{b}=400H_{z},取ξ=0.7,ω_{0}=B_{L}/0.53≈754.7(rad/s),由于采用反正切的鉴别器算法,所以鉴别器的增益k_{d}可取为1,而NCO的控制灵敏度为k_{0}=2πTf_{s}/2^{N},其中,NCO相位累加器的位数设计中N为32,f_{s}为NCO的采样频率,系统中f_{s}为系统时钟60MHz,即为清洗脉冲的周期1/4k秒。从而得到

在用这组值完成频率跟踪后,取窄带的环路滤波器进行相位锁定。这时取B_{L}=0.01R_{b}=40H_{z},此时的计算结果为:C_{1}=1203.9;C_{2}=16.22;快捕带为:10*Hz。

总的来说,环路滤波器系数C_{1}和C_{2}需要根据环路的特性选取,它们值的选取是整个环路跟踪性能的关键。 C_{1}主要决定了环路捕捉带的大小,C_{2}则决定了环路的长期跟踪速度和环路捕获速度。C_{2}较大时,环路将经过相当长的时间才能成功入锁。若用一个固定的环路滤波器,由于锁定时间和精度的不同要求,捕捉时间远小于跟踪时间,这样得到的结果显然不是最优的。为了使环路既具有快速捕获的能力,又能在跟踪状态时仅在平衡点附近有细微摆动,使输出相位平缓变化,故应使环路和步进具有自适应调整的能力。可以采用环路切换法,即在不同时刻转换环路滤波器的参数。

《直扩导航系统中数字科思塔斯环的FPGA设计与实现》相关文章

- › 直扩导航系统中数字科思塔斯环的FPGA设计与实现

- 在百度中搜索相关文章:直扩导航系统中数字科思塔斯环的FPGA设计与实现

- 在谷歌中搜索相关文章:直扩导航系统中数字科思塔斯环的FPGA设计与实现

- 在soso中搜索相关文章:直扩导航系统中数字科思塔斯环的FPGA设计与实现

- 在搜狗中搜索相关文章:直扩导航系统中数字科思塔斯环的FPGA设计与实现

当前位置:

当前位置: