CVSD算法分析及其在FPGA中的实现

[09-12 18:26:41] 来源:http://www.88dzw.com EDA/PLD 阅读:8551次

文章摘要:图4是CVSD译码算法框图,其量阶调整是基于前3位的连码。译码过程就是编码的逆过程,只是在积分器I1后面增加了一个低通滤波器,用于抑制带外干扰。3 CVSD算法在FPGA中的实现3.1 硬件实现框图考虑到实际需求,采用了通用性较强的A/D,D/A元器件和FPGA器件。该硬件可以同时实现3路CVSD编译码算法,一路采用FPGA(XC3S1500)实现,两路采用专用芯片实现;同时编译码之间可以通过FPGA内部逻辑控制互相通信。在FPGA内设计实现了CVSD编译码算法,在该器件内融合多种控制功能,可以在线编程、方便调试。音频信号在进行A/D采样之前,为了防止带外信号进入,首先进行低通滤波;再通过高倍

CVSD算法分析及其在FPGA中的实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com 图4是CVSD译码算法框图,其量阶调整是基于前3位的连码。译码过程就是编码的逆过程,只是在积分器I1后面增加了一个低通滤波器,用于抑制带外干扰。

3 CVSD算法在FPGA中的实现

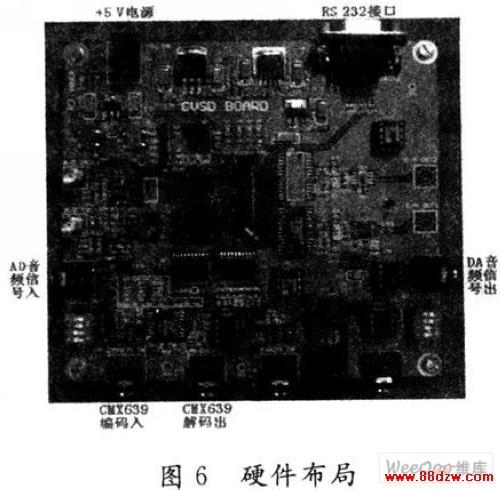

3.1 硬件实现框图

考虑到实际需求,采用了通用性较强的A/D,D/A元器件和FPGA器件。该硬件可以同时实现3路CVSD编译码算法,一路采用FPGA(XC3S1500)实现,两路采用专用芯片实现;同时编译码之间可以通过FPGA内部逻辑控制互相通信。在FPGA内设计实现了CVSD编译码算法,在该器件内融合多种控制功能,可以在线编程、方便调试。

音频信号在进行A/D采样之前,为了防止带外信号进入,首先进行低通滤波;再通过高倍时钟进行采样得到数字信号进入FPGA进行编译码处理。译码过后的信号通过D/A输出模拟信号,该信号再经过低通滤波器后输出,得到音频信号。

3.2 CVSD算法实现框图

在FPGA内部算法实现上,采用了“自顶向下”的设计方法,即根据要求的功能先设计出顶层的原理图,该图由若干个功能模块组成。再把各个模块细化为子模块,各子模块的功能采用电路图实现,也可用硬件描述语言实现。设计中顶层采用原理图实现,子模块采用VHDL硬件描述语言实现,利用ISE自带的IP Core乘法器,经过综合和优化等过程,最终将程序下载到芯片中,使用在线逻辑分析仪ChipScope Pro进行逻辑和功能测试分析。

3.3 CVSD算法的仿真

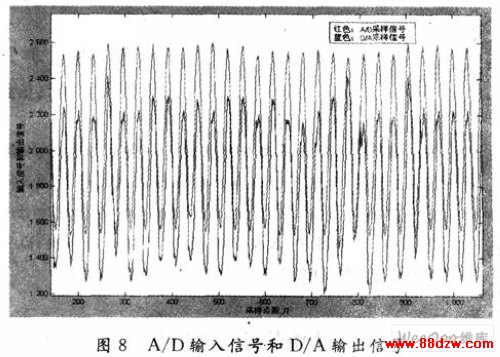

以正弦单音输入信号为例,利用信号源产生信号幅度O.5 Vpp,频率fin(t)=1 kHz的正弦信号作为测试信号,在FPGA中利用高倍时钟产生fs(t)=64 kHz的采样时钟。对输入A/D的音频信号采用专用低通滤波芯片进行了滤波。D/A输出的信号包含了许多不必要的高次谐波分量,因此也采用低通滤波器对其进行了平滑滤波。

在设计上,不仅仅是采用FPGA实现和验证自己的CVSD编译码算法,还和专用芯片CMX639进行互相通信进行验证。CMX639是一款CVSD全双工音频调制芯片,集成了编码和译码功能,实现了单芯片语音处理能力,外围设备简单,用户可以根据实际情况,自主选择采样速率。

图8是通过ChipScope Pro采集的实时正弦信号。从图中可以看出量阶△的大小能够很好地反映输入信号斜率的大小,输出端输出信号能够很好地重现输入信号,说明CVSD编译码方式是有效的。

3.4 CVSD算法的实现

采用原理图和VHDL语言相结合的方式在FPGA中实现了CVSD电路。具体实现步骤如下:

(1)根据算法框图设计顶层原理图CVSD.SCH;

(2)利用IP Core产生底层所需要的乘法器;

(3)利用VHDL语言完成CVSD编译码模块;

(4)I/O管脚定义,约束条件编写;

《CVSD算法分析及其在FPGA中的实现》相关文章

- › CVSD算法分析及其在FPGA中的实现

- 在百度中搜索相关文章:CVSD算法分析及其在FPGA中的实现

- 在谷歌中搜索相关文章:CVSD算法分析及其在FPGA中的实现

- 在soso中搜索相关文章:CVSD算法分析及其在FPGA中的实现

- 在搜狗中搜索相关文章:CVSD算法分析及其在FPGA中的实现

当前位置:

当前位置: