基于FPGA的高速流水线浮点乘法器设计

[09-12 18:26:29] 来源:http://www.88dzw.com EDA/PLD 阅读:8645次

文章摘要:由于 FPGA 具有丰富的与、或门资源,使得该方法在保证速度和准确性的前提下,充分 利用了FPGA 内部资源,节省了面积,同时符合低功耗的要求。3.3 部分积产生与压缩结构设计3.3.1 部分积产生结构根据布思编码器输出结果,部分积产生遵循以下公式【4】:其中,PPi 为部分积;Ai 为被乘数。经过隐藏位和符号位的扩展后,26 位的被乘数尾数将产 生13 个部分积。在浮点乘法器中,尾数运算采用的是二进制补码运算。因此,当NEG=1 时要在部分积的最低位加1,因为PPi 只完成了取反操作。而为了加强设计的并行性,部分 积最低位加1 操作在部分积压缩结构中实现。另外,为了完成有符号数相加,需对部分

基于FPGA的高速流水线浮点乘法器设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com由于 FPGA 具有丰富的与、或门资源,使得该方法在保证速度和准确性的前提下,充分 利用了FPGA 内部资源,节省了面积,同时符合低功耗的要求。

3.3 部分积产生与压缩结构设计

3.3.1 部分积产生结构

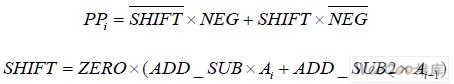

根据布思编码器输出结果,部分积产生遵循以下公式【4】:

其中,PPi 为部分积;Ai 为被乘数。经过隐藏位和符号位的扩展后,26 位的被乘数尾数将产 生13 个部分积。在浮点乘法器中,尾数运算采用的是二进制补码运算。因此,当NEG=1 时要在部分积的最低位加1,因为PPi 只完成了取反操作。而为了加强设计的并行性,部分 积最低位加1 操作在部分积压缩结构中实现。另外,为了完成有符号数相加,需对部分积的 符号位进行扩展,其结果如图4 所示。13 个部分积中,除第一个部分积是29 位以外,其余 部分积扩展为32 位。其中,第一个部分积包括3 位符号扩展位“SSS”,第2 至13 个部分 积的符号扩展位为“SS”,加一操作位为“NN”,遵循如下公式:

其中,i 为部分积的行数,sign(i)为第i 行部分积的符号。

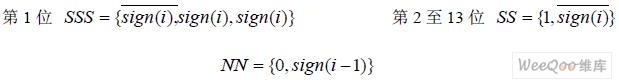

3.3.2 部分积压缩结构

本设计混合使用 4:2 压缩器、3:2 压缩器、全加器和半加器,实现了13 个部分积的 快速压缩,并保证了精度。本文部分积压缩结构的划分如图2 所示。

图 2 中,虚线给出了传统部分积的压缩划分,而实线描述的是本文采用的部分积压缩结 构划分,这样的划分有利于简化第二级的压缩结构,从而在保证速度的基础上,节省FPGA 内部资源。从图2 中可看出,有些位不必计算,因为这些位是由Booth 编码时引入的乘数尾 数的符号位产生的,48 位足以表达运算结果。

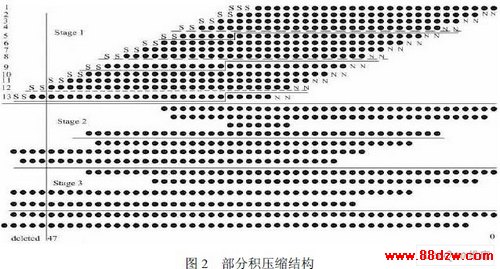

3.3.3 改进的4:2 压缩器

本设计采用广泛使用的 4:2 压缩器,并针对FPGA 内部资源特点,对其进行了改进。 如图3 所示。 传统的 4:2 压缩器即两个全加器级联,共需要四个异或门和8 个与非门。而改进的4: 2 压缩器需要四个异或门和两个选择器(MUX)。8 个与非门需要36 个晶体管,而两个MUX 需要20 个晶体管。同时,FPGA 内部集成了大量的异或门和选择器资源,这种设计方法也是对FPGA 的一个充分利用。

由于压缩部分积需要大量的4:2 压缩器,所以改进的电路能 在一定程度上减小版图的面积,也为该乘法器的ASIC 后端设计带来了优势。另外,改进的 压缩器的4 个输入到输出S 的延时相同,都是3 级XOR 门延时。

4 32 位浮点乘法器的实现与仿真

图 4 显示了本设计的FPGA 时序仿真结果,时序仿真环境为Quartus II 7.0,目标芯片为 Cyclone 系列的EP1C6Q240C8,功能仿真环境为Modelsim 6.0b。整个设计采用VHDL 语言进行结构描述,综合策略为面积优先。由仿真视图可看出,该浮点乘法器可稳定运行在80M 及以下频率,在延时5 个周期后,以后每一个周期可稳定输出一级乘法运算结果,实现了高 吞吐量。如果采用全定制进行后端版图布局布线,乘法器的性能将更加优越。

5 结语

本文作者创新点:针对FPGA 器件内部资源特性,独创地提出了一种适合FPGA 实现 的5 级流水高速浮点乘法器。该乘法器支持IEEE754 标准32 位单精度浮点数,采用了基4 布思算法、改进的布思编码器、部份积压缩结构等组件,从而在保证高速的前提下,缩小了 硬件规模,使得该乘法器的设计适合工程应用及科学计算,并易于ASIC 的后端版图实现。 该设计已使用在笔者设计的浮点FFT 处理器中,取得了良好效果。

《基于FPGA的高速流水线浮点乘法器设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的高速流水线浮点乘法器设计

- 在谷歌中搜索相关文章:基于FPGA的高速流水线浮点乘法器设计

- 在soso中搜索相关文章:基于FPGA的高速流水线浮点乘法器设计

- 在搜狗中搜索相关文章:基于FPGA的高速流水线浮点乘法器设计

当前位置:

当前位置: