基于FPGA的2M误码测试仪设计

[09-12 18:26:25] 来源:http://www.88dzw.com EDA/PLD 阅读:8553次

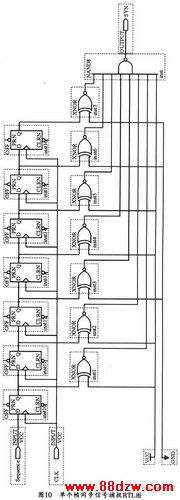

文章摘要:4 结束语本文所介绍的误码测试系统采用以大规模现场可编程逻辑器件FPGA及外围接口芯片构成,文中详细介绍了系统硬件架构中EI接口电路以及FPGA内核中序列发生模块和序列接收模块中核心内容的设计方法,并给出了部分模块的仿真波形。整个误码测试系统仪器结构紧凑。实验表明,该系统在线检测的速度和稳定度方面都有大的提高。上一页 [1] [2] [3] [4]

基于FPGA的2M误码测试仪设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com

4 结束语

本文所介绍的误码测试系统采用以大规模现场可编程逻辑器件FPGA及外围接口芯片构成,文中详细介绍了系统硬件架构中EI接口电路以及FPGA内核中序列发生模块和序列接收模块中核心内容的设计方法,并给出了部分模块的仿真波形。整个误码测试系统仪器结构紧凑。实验表明,该系统在线检测的速度和稳定度方面都有大的提高。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《基于FPGA的2M误码测试仪设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的2M误码测试仪设计

- 在谷歌中搜索相关文章:基于FPGA的2M误码测试仪设计

- 在soso中搜索相关文章:基于FPGA的2M误码测试仪设计

- 在搜狗中搜索相关文章:基于FPGA的2M误码测试仪设计

分类导航

最新更新

当前位置:

当前位置: