基于FPGA嵌入式系统的雷达信号模拟器设计

[09-12 18:26:04] 来源:http://www.88dzw.com EDA/PLD 阅读:8753次

文章摘要:噪声干扰信号的形式比较复杂,主要是通过上位机产生对应的数据,以文本的形式存储下来。在配置FPGA时,将文本文件作为ROM的初始化文件,在编程过程中以查表的形式生成噪声干扰信号。对脉冲雷达距离信息的欺骗主要是通过对收到的雷达照射信号进行延时调制和放大转发来实现。由于单纯的距离质心干扰造成的距离误差较小(小于雷达的距离分辨单元),所以对脉冲雷达距离信息的欺骗主要采用距离假目标干扰和距离波门拖引干扰。距离假目标干扰的模拟在FPGA中体现出来的就是2组重复频率不同的脉冲串,2组脉冲串之间的时间差就对应着延时调制,可以通过计数器控制2个脉冲之间的延迟调制。波门拖引干扰时,通过FPGA控制脉冲宽度和对应的

基于FPGA嵌入式系统的雷达信号模拟器设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com噪声干扰信号的形式比较复杂,主要是通过上位机产生对应的数据,以文本的形式存储下来。在配置FPGA时,将文本文件作为ROM的初始化文件,在编程过程中以查表的形式生成噪声干扰信号。

对脉冲雷达距离信息的欺骗主要是通过对收到的雷达照射信号进行延时调制和放大转发来实现。由于单纯的距离质心干扰造成的距离误差较小(小于雷达的距离分辨单元),所以对脉冲雷达距离信息的欺骗主要采用距离假目标干扰和距离波门拖引干扰。距离假目标干扰的模拟在FPGA中体现出来的就是2组重复频率不同的脉冲串,2组脉冲串之间的时间差就对应着延时调制,可以通过计数器控制2个脉冲之间的延迟调制。波门拖引干扰时,通过FPGA控制脉冲宽度和对应的功率水平,最终将目标回波脉冲分为2个脉冲,且假目标的功率水平比真实目标的功率水平要高。

1.4 实测数据的信号重构

国内在雷达数据采集方面的研究日趋成熟,基于PCI、USB接口的数据采集系统都能满足雷达中视频采样的要求,而且可以根据需要将采集的数据存盘或软件实时回放处理[5-7]。本系统解决的问题是将系统采集到的数据或磁盘阵列上存储的其他系统采集到的雷达实测数据通过模拟系统重构出雷达回波信号,做到真实环境的可重复再现,为雷达接收系统性能的检测提供了有利条件。信号重构过程需要知道雷达回波采样时的采样率,保证模拟系统DA信号输出的速率与数据采集时的采样速率一致,避免采集和恢复速率的不匹配造成雷达信号的非线性失真。同时实测数据帧的组成形式必须是已知的,这样才能提取雷达信号的同步、方位、仰角等信息,将对应的幅度信息与方位、仰角同步。

2 具体实现

2.1 硬件设计

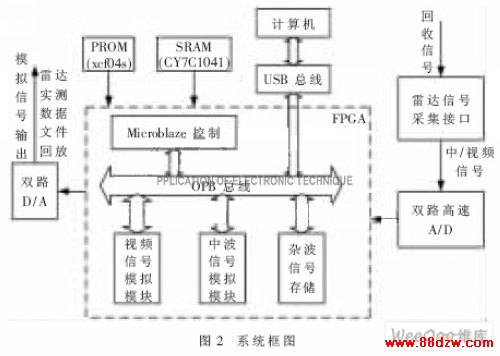

FPGA采用的是Xilinx公司的100万门FPGA芯片XC3S1000,其配置芯片为Xilinx公司的4 MB容量PROM芯片XCF04S,以主动串行方式对FPGA进行上电配置。AD、DA分别为ADI公司12位105 MS/s高速模/数转换芯片AD9432与14位105 MS/s高速数/模转换芯片AD9764。SRAM采用Cypress公司的256k×16 bit SRA。

M芯片CY7C1041用于对数据进行大容量缓存,以满足USB的传输需要。USB控制器选用Cypress公司的EZ-USB FX2系列USB2.0芯片CY7C68013,封装为PQFP128。它支持USB2.0高速传送,最高速率可达480 Mb/s。系统框图如图2所示。

2.2 FPGA程序设计

FPGA程序主要包括雷达信号模拟模块、雷达信号采集与传输控制模块和SDK中Microblaze的控制与参数传递模块。雷达信号模拟模块主要完成对雷达中频/视频和杂波信号的模拟,为雷达的接收系统和信号采集模块提供自检测试信号。雷达信号采集与传输控制模块主要完成对雷达中频/视频信号的采集与传输控制,该模块为系统真实回波的模拟提供了实测数据。参数的传递主要由两部分组成:上位机的信号参数输入或信号模拟系统自带的键盘扫描输入与Microblaze核之间的参数传递;Microblaze将对应的输入参数通过中断调用的形式传递给信号或杂波产生模块。在ISE 9.1环境下通过VHDL硬件语言产生脉冲、LFM等信号,利用EDK 9.1的附件将在ISE 9.1中产生的信号模块转化为对应的IP核[8]。在EDK开发中,可以将在ISE中产生的信号模拟的IP核直接添加到工程中,IP核和Microblaze处理器之间通过OPB总线实现信号参数和中断信号的传递,使整个开发过程模块化。基于FPGA的嵌入式系统设计的EDK开发中有硬件模块设计和软件控制2个部分,使整个系统兼容了FPGA并行处理的高速率和软件编程的简洁。

2.3 驱动程序设计与使用

FX2的设备驱动程序有2种:一种用来在设备接入时从主机下载固件到RAM中,称为固件下载驱动程序(wdgtldr.sys);另一种是在设备重新列举后加载的通用设备驱动程序(ezusb.sys),应用软件通过该设备驱动程序与FX2通信[9]。

固件下载驱动程序(wdgtldr.sys)是利用Cypress公司提供的固件下载驱动程序源代码和用户编译成功的固件代码,在Win2000 DDK中创建的。在将固件代码下载到RAM中后,系统清除内存中的固件下载驱动程序,并进行重新列举,让8051固件控制FX2。此时,系统获得由8051固件提供的新的ID号,认为有新的USB设备接入,并据此加载相应的通用设备驱动程序。通用设备驱动程序一般不需要重新编写,可以直接使用Cypress公司已经编好的驱动程序ezusb.sys。

《基于FPGA嵌入式系统的雷达信号模拟器设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA嵌入式系统的雷达信号模拟器设计

- 在谷歌中搜索相关文章:基于FPGA嵌入式系统的雷达信号模拟器设计

- 在soso中搜索相关文章:基于FPGA嵌入式系统的雷达信号模拟器设计

- 在搜狗中搜索相关文章:基于FPGA嵌入式系统的雷达信号模拟器设计

当前位置:

当前位置: