优化FPGA功耗的设计技术

[09-12 18:25:56] 来源:http://www.88dzw.com EDA/PLD 阅读:8764次

文章摘要:功率监控设计工具市场上涌现了许多以功耗为导向的FPGA设计工具,旨在帮助设计人员在更短的设计周期内实现能效更高的产品。这类EDA工具有两大功能,包括功率驱动布线和功率分析。功率驱动布线 有助于最大限度地降低动态功耗。功率驱动布线工具对功能性实体之间的互连进行分析,并重点优化那些具有很大有效电容乘积(C.f)的网络。同时,这些工具还特别重视时钟网络的横纵时钟源数目,因为这些网络通常是最大且最活跃的。布线后的仿真一般会生成一个VCD文件,用作驱动功率驱动布线的源文件。因为VCD文件报告了设计内部实际的网络开关活动,所以可提供比使用默认普通功率估算更精确的功率分析。为此,首先应该进行时序驱动布局布线

优化FPGA功耗的设计技术,标签:eda技术,eda技术实用教程,http://www.88dzw.com功率监控设计工具

市场上涌现了许多以功耗为导向的FPGA设计工具,旨在帮助设计人员在更短的设计周期内实现能效更高的产品。这类EDA工具有两大功能,包括功率驱动布线和功率分析。

功率驱动布线 有助于最大限度地降低动态功耗。功率驱动布线工具对功能性实体之间的互连进行分析,并重点优化那些具有很大有效电容乘积(C.f)的网络。同时,这些工具还特别重视时钟网络的横纵时钟源数目,因为这些网络通常是最大且最活跃的。

布线后的仿真一般会生成一个VCD文件,用作驱动功率驱动布线的源文件。因为VCD文件报告了设计内部实际的网络开关活动,所以可提供比使用默认普通功率估算更精确的功率分析。为此,首先应该进行时序驱动布局布线,然后反向标注(back annotate),再运行仿真生成VCD文件并导入VCD文件,最后在功率驱动模式下重新运行布局布线。

功率分析 此类工具可用于从功率的角度对设计进行层次化分析,并进一步优化功率。这类工具分析设计层次中的每一个子元素,尤其是功耗排序,一般把功耗最高的功能性实体排在首位。这类信息的仔细分析以及后续设计处理,可以大幅节能。在顶层或所选实体内部,分别标注出由网络、门电路、存储器、I/O、时钟域,或电源轨等因素产生的功耗,这样就可以确定设计内部的功耗热点,设计人员因此能够采取相应措施来降低设计的功耗。

如上所述,设计可能工作在组合模式下。某些功率分析工具能够报告基于功率曲线的平均功耗。在功率曲线中,设计人员规定了设计的工作时间,即活动模式下的时间比例(x%),待机模式下的时间比例(y%),以及Flash*Freeze模式下的时间比例(z%)。分析工具将报告这种组合下的加权平均功耗。在为应用产品选择电池时,这种功能很有用,因为若在节能模式下频繁运作(进入活动模式),电池寿命会大大缩短。

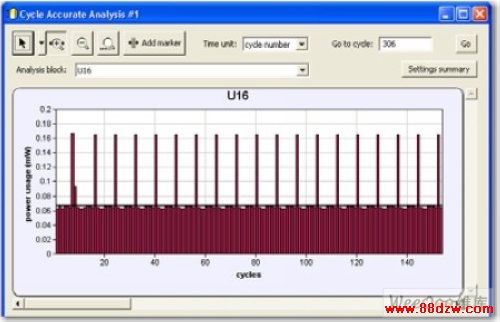

最后,在某些工具中,仿真生成的VCD文件可按时钟周期或时间增量来报告和显示峰值功率。这种功能可帮助用户准确了解什么时间,或哪些时钟周期内功率较高,为设计人员提供另一条应对并可能降低设计功耗的途径(图3)。

图3:FPGA设计中按照时钟周期统计的峰值功率

总结

功耗是基于FPGA系统(尤其是便携式应用)设计人员的主要关注问题。业界领先的FPGA企业相继推出低功耗FPGA架构。EDA工具逐步发展,拥有更复杂完善的架构及功率分析工具,可帮助用户在设计周期的不同阶段*估功耗,并提供具功率监控(power-aware)的综合和布局布线功能。

低功耗设计的第一步是正确选择合适的FPGA技术和器件。良好的设计实践,比如使用门控时钟控制时钟网络、利用FPGA的节能能力,以及对设计进行布图规划,都为具功率意识的设计提供一个框架。功率监控设计工具可通过优化布局布线、功率分析自动化来精细识别功耗热点,让设计人员得以采取纠正措施。通过这些策略、技术和工具,FPGA设计人员就能够降低功耗,最终在节省电池能量或摆脱能源依赖等以后更多的相关课题中发挥重要的作用。

《优化FPGA功耗的设计技术》相关文章

- › 优化FPGA功耗的设计技术

- 在百度中搜索相关文章:优化FPGA功耗的设计技术

- 在谷歌中搜索相关文章:优化FPGA功耗的设计技术

- 在soso中搜索相关文章:优化FPGA功耗的设计技术

- 在搜狗中搜索相关文章:优化FPGA功耗的设计技术

当前位置:

当前位置: