һ�����ڸ��ٸ߾���ADC�ĵ�ѹ��Դ���

[10-10 20:39:48] ��Դ��http://www.88dzw.com ��Դ��· �Ķ���8712��

����ժҪ��0 �������ż��ɵ�·��ģ��������������оƬϵͳ���ɼ������������ģ�⼯�ɵ�·����ģ��(��A��D��D��Aת�������˲����Լ�����ȵ�·)����˸��ߵľ��Ⱥ��ٶ�Ҫ����Ҳ����ζ��ϵͳ�����еĻ�Դģ������˸��ߵ�Ҫ�����ڸ��ٸ߾���ADC��Ƭ�ڵ�ѹ��Դ����Ҫ����ADC���ȺͲ������ʵ�Ҫ��Ӧ���нϵ͵��¶�ϵ���ͽϸߵĵ�Դ���Ʊȣ����⣬���ŵ��ĺͱ�Я��Ҫ��ADCҲ�ڳ��ŵ�ѹ����չ����Ӧ�Ļ�ԴҲҪ����͵�Դ��ѹ��Ҫ���ķ����˻�Դ����ˮ��ADC���ȵ�Ӱ�죬����������Ӧ��ģ�ͣ�ȷ���˸��ٸ߾���ADC�Ե�ѹ��Դ������Ҫ�����˻���1.8 V�ĵ͵�Դ��ѹ�������ýṹ��VBE������

һ�����ڸ��ٸ߾���ADC�ĵ�ѹ��Դ���,��ǩ����Դ��·,��·���,http://www.88dzw.com0 ����

���ż��ɵ�·��ģ��������������оƬϵͳ���ɼ������������ģ�⼯�ɵ�·����ģ��(��A��D��D��Aת�������˲����Լ�����ȵ�·)����˸��ߵľ��Ⱥ��ٶ�Ҫ����Ҳ����ζ��ϵͳ�����еĻ�Դģ������˸��ߵ�Ҫ��

���ڸ��ٸ߾���ADC��Ƭ�ڵ�ѹ��Դ����Ҫ����ADC���ȺͲ������ʵ�Ҫ��Ӧ���нϵ͵��¶�ϵ���ͽϸߵĵ�Դ���Ʊȣ����⣬���ŵ��ĺͱ�Я��Ҫ��ADCҲ�ڳ��ŵ�ѹ����չ����Ӧ�Ļ�ԴҲҪ����͵�Դ��ѹ��Ҫ��

���ķ����˻�Դ����ˮ��ADC���ȵ�Ӱ�죬����������Ӧ��ģ�ͣ�ȷ���˸��ٸ߾���ADC�Ե�ѹ��Դ������Ҫ�����˻���1.8 V�ĵ͵�Դ��ѹ�������ýṹ��VBE�����Զ��ײ�����϶��Դ�ĺ��ĵ�·���ò�����ʽ����ʵ�ֽϵ͵��¶�ϵ������������ٸ߾���ADC��Ҫ����λ�˷Ų���һ�ֵ�������������Ŵ��������˷ſ��ṩС��0.02 mV��ʧ����ѹ�������֤�˻�Դ�IJ������ȡ�Ϊ�����Դ�ĵ�Դ���Ʊȣ����ij����ó��õĹ�Դ��դ�������������⣬�������һ�ּ���Ч�ĵ�Դ���Ʊ���ߵ�·���Ӷ�ʹ�û�Դ�ĵ�Դ���Ʊ����˽ϴ���ߡ�

1 ��ѹ��ԴӰ��Ľ�ģ����

��Pipelined ADCϵͳ�У���Դ����Ҫ������Ϊ��ADC�ṩ�Ƚϵ�ƽ��ͬʱΪMDAC�ṩ�в��ѹ����ֻ���ѹԴ����ƫ�ƻᵼ����ADC�Ƚϵ�ƽ��MDAC�в��ѹ�����仯����ͨ����������λ���������ɴ���С��ֻ���ѹԴ������ıȽϵ�ƽ�仯��ϵͳָ����ɵ�Ӱ�죬���ǣ�MDAC�в��ѹ�仯��Ӱ��ȴ��������ϵͳ��ת�����������Խ��ᷢ���仯���Ӷ����ϵͳָ���½������л���ѹԴ��ƫ����Ҫ��Դ���¶Ⱥ͵�Դ��ѹ��Ӱ�졣

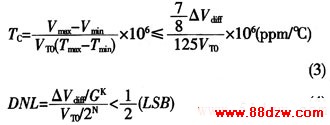

�����������ѹԴ�¶�Ư�����Զ�DNL��Ӱ�졣һ������£�ʵ����������������������֮���ƫ����Ա�ʾΪ��

����������Ϊ3.5λ��12λADC����-40�桫85����¶ȷ�Χ�ڣ����¶�Ҫ�����ϸ�ıȽ���һ��Ҫ�����ѹԴ�������Ư������(7��8)Vdiff��

����������ʽ��

���Եõ�DNL�Ի���ѹԴ�¶�ϵ����Ҫ���¶�ϵ��TC��6.84 ppm���档ʽ�У�VT0Ϊ����25��ʱ�Ļ���ѹֵ��

2��ѹ��Դ��·�ṹ���

2.1 �������ʲ�������

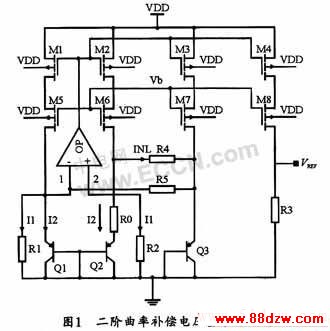

��ǰ�ķ�����֪��12λADCϵͳҪ���¶�ϵ��ӦС��6.84ppm��K���ܴﵽ12λ���ȡ���ͳ��϶��Դ���Ѵﵽ���Ҫ����ˣ�����ѡ��һ����ͼ1��ʾ�Ķ������ʲ����ĵ�ѹ��Դ�ṹ��

��ͼ1��ʾ������VBE���¶ȹ�ϵʽ��

www.88dzw.com2.3 ��ߵ�Դ���Ʊȵĵ�·���

��϶����·�ĵ�Դ��ѹ���Ʊȿ��Ա�ʾΪ��PSRR=�O(1-Add)��AV�O������AVΪ�˷ŵĿ������棬AddΪ�˷ŵ�������Դ��Ndd֮�ȡ���ˣ�Ϊ�����PSRR�����Բ�ȡ���ִ�ʩ��һ�������˷ŵĿ�������Av�����ǸĽ���·�ṹʹ�˷ŵ�A

Tag:��Դ��·����Դ��·,��·������ҵ�ά�� - ��Ԫ��·���� - ��Դ��·

��һ�����ڸ��ٸ߾���ADC�ĵ�ѹ��Դ��ơ��������

- › һ�����ڸ��ٸ߾���ADC�ĵ�ѹ��Դ���

- › һ������������ŷ��������Ե�Դ�����

- › һ�������ֳ��ƶ��ն˵Ŀ��ع��������

- › һ�����ں����״﹩��IJ��ϵͳ���

- �ڰٶ�������������£�һ�����ڸ��ٸ߾���ADC�ĵ�ѹ��Դ���

- �ڹȸ�������������£�һ�����ڸ��ٸ߾���ADC�ĵ�ѹ��Դ���

- ��soso������������£�һ�����ڸ��ٸ߾���ADC�ĵ�ѹ��Դ���

- ���ѹ�������������£�һ�����ڸ��ٸ߾���ADC�ĵ�ѹ��Դ���

���ർ��

���¸���

- �� �����ܵ�����﮵�س�����оƬCN3052A/CN

- �� ����LTC3615��Ƶ�˫·3Aͬ����ѹ����

- �� ����NCP1031��Ƶ���̫������DC-DCת������

- �� ��Яʽϵͳѡ���Դ���˷����ķ������Ա�

- �� ��δ���̫�����磨PoE����ø�����

- �� �������������ķ���ͬ���������Ƶ�·

- �� ������ԴLED������������

- �� ���ص�Դ����EMI�˲�����������

- �� �������ּ��ɵ�·�İ뵼�弤������Դ�����

- �� �������˲������Դ�������ѹ��Դ����ԭ��

��ǰλ�ã�

��ǰλ�ã�