基于FPGA的工控领域监控系统设计

[10-10 20:39:48] 来源:http://www.88dzw.com 电源电路 阅读:8779次

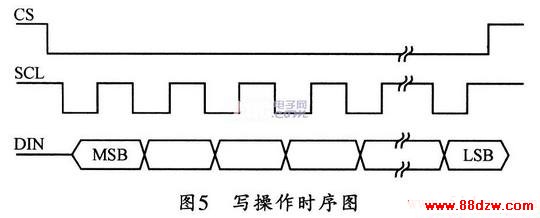

文章摘要: 第二个是设置寄存器,用于决定校准模式、增益设置、单/双极性输入以及缓冲模式; 第三个是时钟寄存器,其中包括滤波器选择位和时钟控制位; 第四个是数据寄存器,器件输出的数据从这个寄存器读出; 第五个是零标度校准寄存器,AD7705包含两组独立的零标度寄存器,每个零标度寄存器负责一个输入通道。它们都是24位读,写寄存器; 第六个是满标度校准寄存器,AD7705包含两组独立的满标度寄存器,每个满标度寄存器负责一个输入通道。它们都是24位读/写寄存器。 AD7705的写操作时序图如图5所示。在将片选端CS拉低后,即可在串行时钟的上升沿发送数据,发送数据时,高位在前。

基于FPGA的工控领域监控系统设计,标签:电源电路,电路设计,http://www.88dzw.com第二个是设置寄存器,用于决定校准模式、增益设置、单/双极性输入以及缓冲模式;

第三个是时钟寄存器,其中包括滤波器选择位和时钟控制位;

第四个是数据寄存器,器件输出的数据从这个寄存器读出;

第五个是零标度校准寄存器,AD7705包含两组独立的零标度寄存器,每个零标度寄存器负责一个输入通道。它们都是24位读,写寄存器;

第六个是满标度校准寄存器,AD7705包含两组独立的满标度寄存器,每个满标度寄存器负责一个输入通道。它们都是24位读/写寄存器。

AD7705的写操作时序图如图5所示。在将片选端CS拉低后,即可在串行时钟的上升沿发送数据,发送数据时,高位在前。

AD7705的读操作时序图如图6所示。当在AD7705的DRDY信号脚检测到逻辑低电平时,表示可以从AD7705的数据寄存器获取新的输出字,当完成对一个完全的输出字的读操作后,DRDY引脚立即回到高电平。如果在两次输出更新之间,不发生数据输出,DRDY将在下一次输出更新前500个输入时钟时间返回高电平。DRDY处于高电平时,不能进行读操作。当数据更新后,DRDY又返回低电平。

2.2 FPGA接口的软件设计

FPGA与AD7705共有5个接口引脚,分别为片选端CS、串行时钟端SCLK、串行数据输入端DIN、串行数据输出端DOUT和串行数据请求端

DRDY。

读AD7705的数据寄存器前,需先设置其时钟寄存器和设置寄存器,下面以1通道为例来简要说明,首先向AD7705发送串行数据0x20,表示下一操作选择时钟寄存器,接着发送串行数据0x0C,设置时钟为2分频,然后发送Oxl0,表示下一操作选择设置寄存器,接着发送串行数据0x44,表示设置寄存器模式为自校准,增益l,单极性,无缓冲,然后再向AD7705发送0x38,表示可以读通道1的数据寄存器,并等待AD7705的DRDY变低,然后发送16个时钟,以读取通道1的16位转换数据。通道2的数据读取与通道1的数据读取相似,发送的数据分别为0x21,0x0C,

0x11,0x44,0x39。

3 结束语

本文用有限状态机在FPGA上实现了对有SPI接口的AD转换器AD7705的接口应用,并对AD7705的两路输入信号进行了实时采集。事实上,选用通用I/O口模拟SPI时序,相比标准SPI接口IP核更为简洁,可以节约FPGA的片上资源。由于AD7705提供有双通道、低成本、高分辨率的模数转换功能,因此,采用∑-△结构实现模数转换,可使得该器件在噪音环境下免受干扰,因而很适合于工业控制应用。

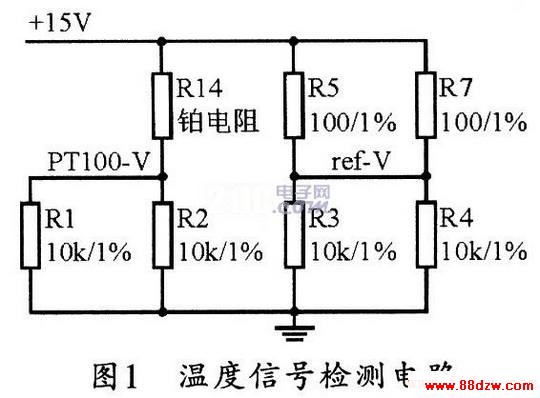

1.2 温度信号转换电路

图1所示是本系统中的温度信号检测电路。

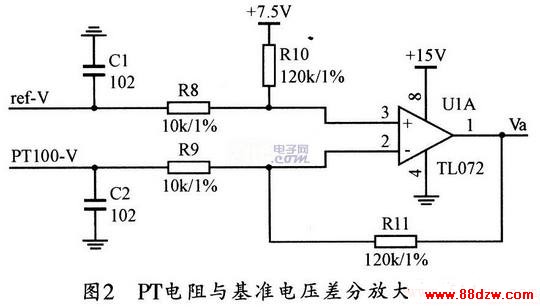

图1电路中,R14是放在散热器表面的铂电阻,用于感应散热器的温度,该电路可将PT电阻随温度信号变化的阻值信号转变成电压信号,这样,根据PTl00-V点的电压值,即可换算出PT电阻R14的电压信号,ref-V为基准电压信号,ref-V经过图2所示的差分放大电路后,再根据图中元器件的参数即可计算出,最后传输的电压信号Va为与基准电压差值的12倍。

- 上一篇:低压CM0S带隙基准电压源设计

《基于FPGA的工控领域监控系统设计》相关文章

- › 基于FPGA的1553B通信模块的设计

- › 基于FPGA的工控领域监控系统设计

- › 基于FPGA的嵌入式系统USB接口设计

- › 基于FPGA的NAND Flash ECC校验

- › 基于FPGA的实时中值滤波器硬件实现

- › 一种基于FPGA控制全彩大屏幕显示的设计

- 在百度中搜索相关文章:基于FPGA的工控领域监控系统设计

- 在谷歌中搜索相关文章:基于FPGA的工控领域监控系统设计

- 在soso中搜索相关文章:基于FPGA的工控领域监控系统设计

- 在搜狗中搜索相关文章:基于FPGA的工控领域监控系统设计

当前位置:

当前位置: