简易通用型PCI接口的VHDL-CPLD设计

[11-20 16:13:47] 来源:http://www.88dzw.com FPGA 阅读:8182次

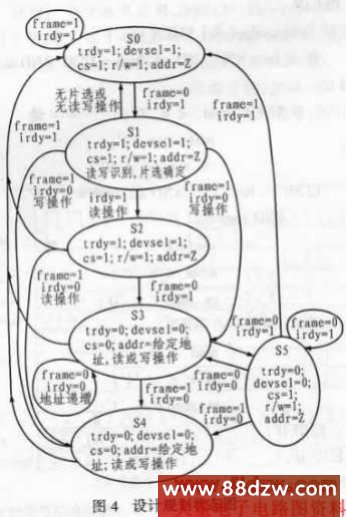

文章摘要:状态S5用于对PCI总线置低信号TRDY和DEVSEL;并且对双口RAM置高片选信号CS,以使读/写信号处于读状态,此时地址呈现三态。 3.3 状态变化的确定 根据对PCI总线传输时序的分析,影响各个状态相互转化的因素是:帧同步信号FRAME、主设备准备好信号IRDY、从设备选择信号CS-MAP、读识别信号READ以及写识别信号WRITE。这里,可用CS-MAP、READ、WRITE来标识状态S1产生的中间识别信号。 图3 需要注意,在状态S1时要寄存收到的首地址,而在状态S3变化时要适时进行地址递增。 还要注意状态机设计时产生的容错问题,以便在非设计状态下能够无条件回到空闲态S0。 由于采用

简易通用型PCI接口的VHDL-CPLD设计,标签:fpga是什么,fpga教程,http://www.88dzw.com状态S5用于对PCI总线置低信号TRDY和DEVSEL;并且对双口RAM置高片选信号CS,以使读/写信号处于读状态,此时地址呈现三态。

3.3 状态变化的确定

根据对PCI总线传输时序的分析,影响各个状态相互转化的因素是:帧同步信号FRAME、主设备准备好信号IRDY、从设备选择信号CS-MAP、读识别信号READ以及写识别信号WRITE。这里,可用CS-MAP、READ、WRITE来标识状态S1产生的中间识别信号。

图3

需要注意,在状态S1时要寄存收到的首地址,而在状态S3变化时要适时进行地址递增。

还要注意状态机设计时产生的容错问题,以便在非设计状态下能够无条件回到空闲态S0。

由于采用的是高速双口RAM,并且规划分开了RAM两侧的写操作区域,因此可以认为:RAM是可以任意访问的。

3.4 状态图的规划

综上所述便可得出如图4所示的设计规划图。

4 VHDL语言的描述

设计时,使用三个进程和几个并行语句可实现整个CPLD的功能:一个进程用于完成从设备及其读写操作的识别;一个进程用于完成操作地址的获取与地址的递增;第三个进程完成状态机的变化。用几个并行语句完成操作信号的产生时,需要注意,各状态所完成的功能要用并行语句实现,不能再用进程,否则就会引起逻辑综合的麻烦,有时甚至根本不能综合。整 个程序如下:

LIBRARY ieee;

USE ieee.std_logic_1164.All;

USE ieee.std_logic_unsigned.ALL;

ENTTTY cpci IS

PORT(clk,rst,frame,irdy:IN STD_LOGIC;

ad_high : IN STD_LOGIC_VECTOR(31 downto 24);

ad_low : IN STD_LOGIC_VECTOR(12 downto 0);

c_be : IN STD_LOGIC_VECTOR(3 downto 0);

trdy,devsel:OUT STD_LOGIC;

cs, r_w :OUT STD-LOGIC;

addr: OUT STD_LOGIC_VECTOR(12 downto 0);

END cpci;

ARCHITECTURE behave OF cpci IS

SIGNAL addr_map : STD_LOGIC_VECTOR(12 downto 0);

SIGNAL read,write,cs-map:STD_LOGIC;

TYPE state_type IS(s0,s1,s2,s3,s4,s5);

SIGNAL state: state_type;

BEGIN

Identify: PROCESS(clk)- -读、写、从设备的识别

BEGIN

IF rising_edge(clk)THEN

IF c_be=X"6"AND ad_high=X"50"AND state=s1

HTEN read < = '0'; - -读

write < = '1';

cs_map < ='0';

ELSIF c_be=X"7"AND ad_high= X"50"

AND state=s1 THEN

read < = '1'; - -写

write < = '0';

cs_map < ='0';

ELSIF state=s0 THEN

read < = '1';

write < = '1';

cs_map < ='1';

END IF;

END IF;

END PROCESS;

Addr_count:PROCESS (clk) - -操作地址的获取与地址的递增

BEGIN

IF falling_edge(clk)THEN

IF state=s1 THEN addr_map< =ad-low;

ELSIF state=s3 THEN addr_map< =addr-map+1;

《简易通用型PCI接口的VHDL-CPLD设计》相关文章

- › 简易通用型PCI接口的VHDL-CPLD设计

- 在百度中搜索相关文章:简易通用型PCI接口的VHDL-CPLD设计

- 在谷歌中搜索相关文章:简易通用型PCI接口的VHDL-CPLD设计

- 在soso中搜索相关文章:简易通用型PCI接口的VHDL-CPLD设计

- 在搜狗中搜索相关文章:简易通用型PCI接口的VHDL-CPLD设计

当前位置:

当前位置: