基于FPGA的快速9/7整形离散小波变换系统设计

[09-12 18:35:18] 来源:http://www.88dzw.com EDA/PLD 阅读:8156次

文章摘要:2.2 列变换过程由于列变换是针对行变换后的数据进行的,即对上面6片RAM中存储的行变换后的数据进行列变换,为了提高运行速度,本文采用基于行的列变换方法,即当小波变换进行到第5行时,列变换也同时进行,第5行行变换结束时,也完成了针对第5行数据的列变换,当第6行进行小波变换时,不进行列变换操作,直到第7行小波行变化数据输入时,再同时进行列变换计算操作,依次完成小波列变换。对于列小波变换后的低频数据dLLl,要输入RAM缓存以进行下一级变换,对于其他的高频数据(dLHl,dHLl,dHHl)可以直接输出到片外存储器中。下面是设计的一级二维小波变换的集成模块,如图5所示。3 仿真与综合为了验证本文设

基于FPGA的快速9/7整形离散小波变换系统设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com2.2 列变换过程

由于列变换是针对行变换后的数据进行的,即对上面6片RAM中存储的行变换后的数据进行列变换,为了提高运行速度,本文采用基于行的列变换方法,即当小波变换进行到第5行时,列变换也同时进行,第5行行变换结束时,也完成了针对第5行数据的列变换,当第6行进行小波变换时,不进行列变换操作,直到第7行小波行变化数据输入时,再同时进行列变换计算操作,依次完成小波列变换。对于列小波变换后的低频数据dLLl,要输入RAM缓存以进行下一级变换,对于其他的高频数据(dLHl,dHLl,dHHl)可以直接输出到片外存储器中。

下面是设计的一级二维小波变换的集成模块,如图5所示。

3 仿真与综合

为了验证本文设计系统的性能,使用Modlesim6.3仿真软件对系统进行了仿真测试,下面是采用大小为1 024×1 024,图像数据为8位的测试图像进行测试仿真的部分波形图。

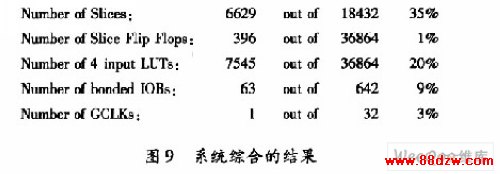

在Xilinx提供的ISE7.1仿真软件下搭建测试平台,对设计系统进行综合,结果如图9所示。

设计系统时钟频率可达到54 MHz,满足对图像数据的实时处理要求。

4 结束语

本文主要讨论了基于FPGA的快速9/7整形离散小波变换系统设计,该结构采用内部RAM的循环覆盖的存储方式,使对存储器的需求量减小,从而减小了硬件功耗,同时采用基于行的列变换方式,提高了的系统运行,可实现对遥感传输图像的快速实时处理。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

- 上一篇:基于FPGA的UART设计与实现

《基于FPGA的快速9/7整形离散小波变换系统设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的快速9/7整形离散小波变换系统设计

- 在谷歌中搜索相关文章:基于FPGA的快速9/7整形离散小波变换系统设计

- 在soso中搜索相关文章:基于FPGA的快速9/7整形离散小波变换系统设计

- 在搜狗中搜索相关文章:基于FPGA的快速9/7整形离散小波变换系统设计

分类导航

最新更新

当前位置:

当前位置: