基于FPGA的数字脉冲压缩系统实现

[09-12 18:35:01] 来源:http://www.88dzw.com EDA/PLD 阅读:8937次

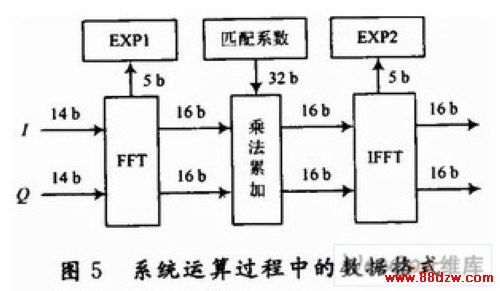

文章摘要:ADC输入数据为14 b的二进制补码形式,对其低位补零扩展为16 b(IP核要求的输入精度)后送入FFT运算单元,输出结果为16 b的定点数以及指数EXP1。复乘包括乘法和累加运算,即FFT结果与匹配系数进行16 b×16 b的乘法运算,所得结果再进行加法运算;在进行加法运算前,所有数据扩展为33 b以防止溢出的发生,最终数据截取高16 b送入IFFT处理单元,输出为16 b的定点数和指数EXP2,将其与EXPl相加后得到指数EXP。脉压的最终结果即为IFFT后的16 b定点数以及指数EXP,两者分别存储在FPGA片内RAM中。2.3 脉冲压缩模块的测试设输入理想LFM信号参数如下:带宽B=4

基于FPGA的数字脉冲压缩系统实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com

ADC输入数据为14 b的二进制补码形式,对其低位补零扩展为16 b(IP核要求的输入精度)后送入FFT运算单元,输出结果为16 b的定点数以及指数EXP1。复乘包括乘法和累加运算,即FFT结果与匹配系数进行16 b×16 b的乘法运算,所得结果再进行加法运算;在进行加法运算前,所有数据扩展为33 b以防止溢出的发生,最终数据截取高16 b送入IFFT处理单元,输出为16 b的定点数和指数EXP2,将其与EXPl相加后得到指数EXP。脉压的最终结果即为IFFT后的16 b定点数以及指数EXP,两者分别存储在FPGA片内RAM中。

2.3 脉冲压缩模块的测试

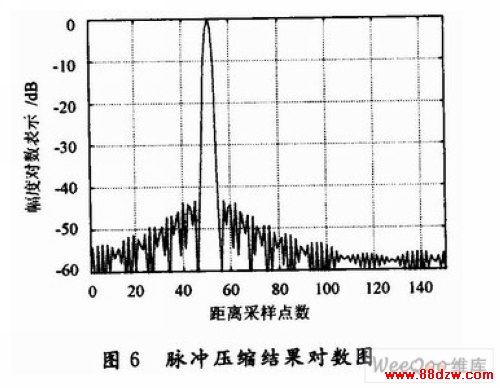

设输入理想LFM信号参数如下:带宽B=40 MHz;时宽T=6μs;系统样本速率为60 MHz;使用海明窗加权。在上述条件下,脉冲压缩系统的输出结果对数图如图6所示。

在图6中,横轴代表距离采样单元,即系统最小距离分辨率。通过系统实际处理结果与Madab仿真结果的对比验证了设计的正确性和实用性。

3 结语

系统采用ADS5500完成14位、60 MSPS的数据采集,并在FPGA中实现1 024点的数字脉冲压缩。设计采用并行流水方式提高工作速度,而块浮点算法则充分保证运算的精度。IP核的复用大大降低硬件规模,从而使整个系统具有高速度、高精度和低功耗的特点。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《基于FPGA的数字脉冲压缩系统实现》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的数字脉冲压缩系统实现

- 在谷歌中搜索相关文章:基于FPGA的数字脉冲压缩系统实现

- 在soso中搜索相关文章:基于FPGA的数字脉冲压缩系统实现

- 在搜狗中搜索相关文章:基于FPGA的数字脉冲压缩系统实现

分类导航

最新更新

当前位置:

当前位置: