基于FPGA的Viterbi译码器设计

[09-12 18:33:37] 来源:http://www.88dzw.com EDA/PLD 阅读:8748次

文章摘要:摘要:卷积码及其Viterbi译码是现代通信系统中常用的一种信道编码方法。文中介绍了Viterbi译码算法的原理,分析了Viterbi译码器的结构,然后用Verilog语言设计了一种基于Altera公司的EP3C120F780C8芯片的(2,l,7)Viterbi译码器,同时给出了时序仿真图。0 引言在现代通信系统中,要使信号能够更可靠地在信道中传输,往往需要我们在信道编码中采用纠错码来降低信号受噪声的影响,以降低传输的误码率。这种方法叫做差错控制编码或纠错编码,其思想是在发送端的信息码元序列中增加一些监督码元,这些监督码与信码之间有一定的关系,接收端可以利用这种关系由信道译码器来发现或纠正错

基于FPGA的Viterbi译码器设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com摘要:卷积码及其Viterbi译码是现代通信系统中常用的一种信道编码方法。文中介绍了Viterbi译码算法的原理,分析了Viterbi译码器的结构,然后用Verilog语言设计了一种基于Altera公司的EP3C120F780C8芯片的(2,l,7)Viterbi译码器,同时给出了时序仿真图。

0 引言

在现代通信系统中,要使信号能够更可靠地在信道中传输,往往需要我们在信道编码中采用纠错码来降低信号受噪声的影响,以降低传输的误码率。这种方法叫做差错控制编码或纠错编码,其思想是在发送端的信息码元序列中增加一些监督码元,这些监督码与信码之间有一定的关系,接收端可以利用这种关系由信道译码器来发现或纠正错误的码元。

1 卷积码

前向纠错(FEC)是目前常用的一种差错控制方法,在这种方法中,发送端发送能够被纠错的码,接收端则在收到这些码后,通过纠错译码器来发现其中的错误并自动纠正接收码字中的错误。在前向纠错方法中,卷积码及其Viterbi译码是常用的信道编码方案。

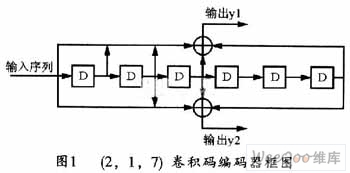

卷积码通常用(n,k,N)表示,其中n为输出信息比特,k为输入信息比特,N为约束长度,卷积码的编码效率为Rc=k/n,图1所示为(2,l,7)卷积码的编码器框图。

(2,1,7)卷积码编码器由6个延时器(图1中的D模块,可用寄存器实现)和两个模二加法器组成,它的编码约束度为7,码率为1/2。即输入端输入1比特信息,输出端输出2比特编码信息,并分为上、下两路并行输出。

2 Viterbi译码器原理

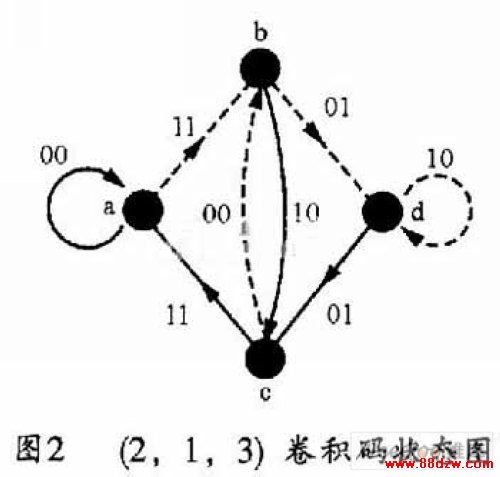

近年来,维特比算法具有很大的发展,目前在数字通信的前向纠错系统中用的较多。Viterbi译码的基本原理是把已接收到的序列与所有可能的发送序列进行比较,选择其中码距最小的一个序列作为发送序列。下面以(2,1,3)卷积码编码器的编出码为例,来说明Viterbi解码的方法和过程。图2所示是该码的状态图。

结合状态图可得出如图3所示的状态与时间关系图,称为网格图。该图设输入信息数目L=5,所以画有L+N=8个时间单位(节点),图3中分别标以0至7。设编译器从a状态开始运作。该网格图的每一条路径都对应着不同的输入信息序列。由于所有的可能输入信息序列共有2KL个,因而其网格图中所有可能的路径也是2KL条。

设编译器送出的码序列为C,经过离散无记忆信道传输后送入译码器的是序列R,E是信道错误序列,则有:R=C+E。译码器根据接收序列R,可以按最大似然估计准则来找出编码器在网格图上所走过的路径,这个过程就是译码器计算、寻找的最大似然函数:

经计算可得,上式等价于寻找与R有最小汉明距离的路径,即寻找:

对于二进制输入且Q进制输出的离散无记忆信道,实际上就是寻找与R有最小软距离的路径,而此时的度量就是软判决距离:

《基于FPGA的Viterbi译码器设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的Viterbi译码器设计

- 在谷歌中搜索相关文章:基于FPGA的Viterbi译码器设计

- 在soso中搜索相关文章:基于FPGA的Viterbi译码器设计

- 在搜狗中搜索相关文章:基于FPGA的Viterbi译码器设计

当前位置:

当前位置: