基于FPGA的DDR内存条的控制研究

[09-12 18:33:31] 来源:http://www.88dzw.com EDA/PLD 阅读:8818次

文章摘要:摘要:随着数据存储量的日益加大以及存储速度的加快,大容量的高速存储变得越来越重要。内存条既能满足大容量的存储又能满足读写速度快的要求,这样使得对内存条控制的应用越来越广泛。首先介绍了内存条的工作原理,内存条电路设计的注意事项,以及如何使用FPGA实现对DDR内存条的控制,最后给出控制的仿真波形。1 内存条的工作原理DDR内存条是由多颗粒的DDR SDKAM芯片互连组成,DDR SDRAM是双数据率同步动态随机存储器的缩写。DDR SDRAM采用双数据速率接口,也就是在时钟的正沿或负沿都需要对数据进行采样。在本设计中采用的内存是hynix公司的lGB的HYMD564M646CP6-J。内存条的工

基于FPGA的DDR内存条的控制研究,标签:eda技术,eda技术实用教程,http://www.88dzw.com摘要:随着数据存储量的日益加大以及存储速度的加快,大容量的高速存储变得越来越重要。内存条既能满足大容量的存储又能满足读写速度快的要求,这样使得对内存条控制的应用越来越广泛。首先介绍了内存条的工作原理,内存条电路设计的注意事项,以及如何使用FPGA实现对DDR内存条的控制,最后给出控制的仿真波形。

1 内存条的工作原理

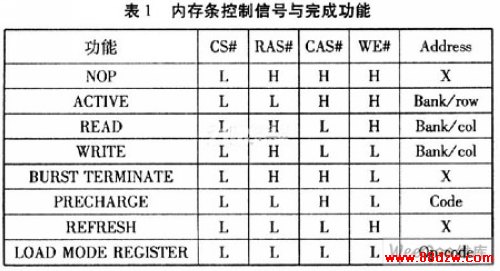

DDR内存条是由多颗粒的DDR SDKAM芯片互连组成,DDR SDRAM是双数据率同步动态随机存储器的缩写。DDR SDRAM采用双数据速率接口,也就是在时钟的正沿或负沿都需要对数据进行采样。在本设计中采用的内存是hynix公司的lGB的HYMD564M646CP6-J。内存条的工作原理与单颗粒内存芯片的工作原理一样,主要的控制信号以及控制信号完成的主要功能如表1所示。

以上的控制信号及地址信号都是由差分时钟信号中CK的正沿触发。DDR SDRAM必须按照一定的工作模式来完成初始化,完成初始化后才能进入到读写过程。DDR SDRAM的控制流程如图1所示。

初始化的过程为:(1)上电后,延时200us等待时钟稳定,然后将CKE拉高,执行一次NOP或者DESELECT操作。(2)执行一次precharge all操作。(3)设置扩展模式寄存器(BAl为低电平BA0为高电平)使能DLL。(4)设置模式寄存器(BAl,BA0均为低电平)复位DLL。(5)执行一次pre-charge all指令。(6)再经过2个自刷新(Auto refresh)指令后再次设置模式寄存器设置操作模式。(7)延时200个周期才能进行读操作。DDR SDRAM的扩展模式寄存器和模式寄存器的定义如图2和图3所示。

完成初始化后进入图1中的IDEL状态,此时可以进行读写操作。在进行写操作时,首先要进入Row active状态,此时选中要操作的bank与row。然后执行NOP操作等待tRCD的时间后可以进入写状态。

2 内存条电路设计

由于DDR SDRAM采用的时钟频率较高,加上DDRSDRAM的数据率为时钟速率的两倍,DDR SDRAM对时钟质量的要求很高,必须保证时钟上升沿的时间小于5%的时钟周期。DDR SDRAM的数据线与相对应的数据采样信号(DQS)的长度要尽量相等,来保证数据的采样窗口尽量要大一些。由于信号质量要求高,我们将所有的信号线都采用微电线和带状线来传输。使用FPGA和内存条的IBIS模型进行仿真来保证设计中信号的完整性,我们将信号分为3类,第一类,由FPGA到DDR SDRAM的时钟差分信号;第二类,由FPGA到DDR SDRAM的控制线;第三类,FPGA与DDR SDRAM之间的双向传输线。对三类IBIS模型的herperlinx仿真如图4:

通过仿真我们可以确定3类信号线中带状线和微带线板厚,铜厚,以及信号线的线宽,线长等参数。

3 FPGA对DDR SDRAM的控制

本设计中使用的FPGA是ALTERA公司的cyclone II系列的EP2C20F484C6。对内存条的工作模式设置为BL=4,CL=3,如图7为FPGA对DDR SD-RAM的控制模块框图。

《基于FPGA的DDR内存条的控制研究》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的DDR内存条的控制研究

- 在谷歌中搜索相关文章:基于FPGA的DDR内存条的控制研究

- 在soso中搜索相关文章:基于FPGA的DDR内存条的控制研究

- 在搜狗中搜索相关文章:基于FPGA的DDR内存条的控制研究

当前位置:

当前位置: