基于FPGA的二-十进制转码器设计

[09-12 18:32:57] 来源:http://www.88dzw.com EDA/PLD 阅读:8286次

文章摘要:为了克服以上的转码器设计缺陷,针对FPGA的结构特点,笔者提出了以下设计思路:(1)以4 bit数据转换作为基本的转换单元来适应FPGA结构特点,而提高逻辑单元利用率,达到降低硬件代价的目的;(2)利用Verilog HDL层次化设计描述的灵活性,以4 bit数据转换单元为最底层模块,构造出更大的5 bit和6 bit转换单元(模块)。这种设计方法为二-十进制(BCD)转码器的构建提供了4 bit、5 bit和6 bit三种不同大小的单元模块,可使每一个转换单元模块的使用恰到好处(需要小模块的地方就不会使用大模块)。2.2.1 二-十进制(BCD)转码器单元模块设计采用上文所述基于FPGA的二

基于FPGA的二-十进制转码器设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com为了克服以上的转码器设计缺陷,针对FPGA的结构特点,笔者提出了以下设计思路:(1)以4 bit数据转换作为基本的转换单元来适应FPGA结构特点,而提高逻辑单元利用率,达到降低硬件代价的目的;(2)利用Verilog HDL层次化设计描述的灵活性,以4 bit数据转换单元为最底层模块,构造出更大的5 bit和6 bit转换单元(模块)。这种设计方法为二-十进制(BCD)转码器的构建提供了4 bit、5 bit和6 bit三种不同大小的单元模块,可使每一个转换单元模块的使用恰到好处(需要小模块的地方就不会使用大模块)。

2.2.1 二-十进制(BCD)转码器单元模块设计

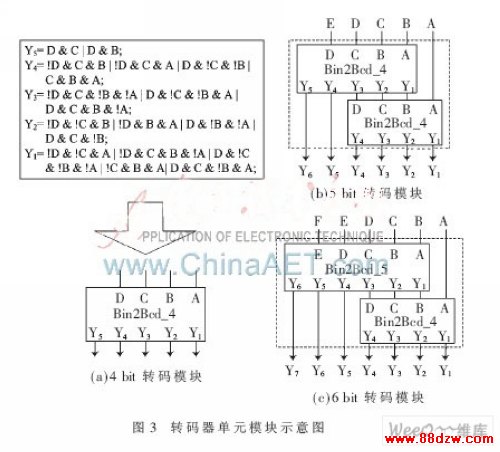

采用上文所述基于FPGA的二-十进制(BCD)转码器设计方案,关键在于要做好最底层模块(4 bit转码模块)的优化设计,对4 bit转码模块的不同Verilog HDL描述方式也会带来不同的实现代价;本文使用结构描述实现4 bit转码模块(Bin2Bcd_4),再通过4 bit转码模块层次实例化构成5 bit转码模块(Bin2Bcd_5)和6 bit转码模块(Bin2Bcd_6)的设计,4 bit、5 bit和6 bit三种单元模块的构造示意图如图3所示。

2.2.2 基于混合模块的二-十进制(BCD)转码器设计

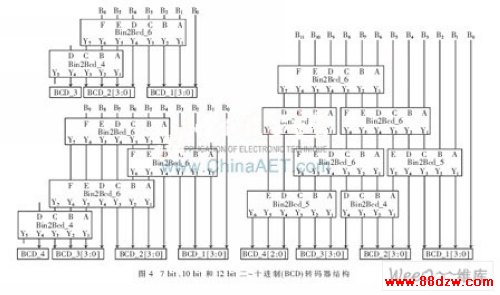

根据二-十进制(BCD)转码算法,使用上文2.2.1中得到的4 bit、5 bit和6 bit三种二-十进制转码单元模块,构造出7 bit、10 bit和12 bit二-十进制(BCD)转码器结构,如图4所示,转码单元模块的多余输入端接地,多余输出端悬空。

3 二-十进制(BCD)转码器的设计验证

本文使用Quartus II 6.0(Full Version)开发工具,对于图4所示的3个混合模块构建的二-十进制(BCD)转码器,在Altera公司的FPGA(Altera EP1K30QC208-2)芯片上分别进行了设计验证,验证结果完全达到设计预期。其中12 bit二-十进制(BCD)转码器的功能仿真和时序仿真结果如图5所示。

在完全相同的软硬件验证环境下,把图4所示的转码器设计和使用中规模集成电路IP核(SN74185A)实现的7 bit、10 bit和12 bit的转码器进行了性能对比,验证结果进一步表明了这种采用混合模块构建二-十进制(BCD)转码器的行之有效性;表1所示为采用这两种构建方法得到的7 bit、10 bit和12 bit转码器的验证结果对比。

Altera EP1K30QC208-2(FPGA)芯片上的7 bit、10 bit和12 bit转码器设计验证结果和使用IP核(SN74185A)实现的转码器验证结果对比更加充分证明了这种设计思路的可行性;这种高效、易于重构的二-十进制(BCD)转码器设计为基于FPGA的片上数字测量系统实现做出了有意义的积极探索。

《基于FPGA的二-十进制转码器设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的二-十进制转码器设计

- 在谷歌中搜索相关文章:基于FPGA的二-十进制转码器设计

- 在soso中搜索相关文章:基于FPGA的二-十进制转码器设计

- 在搜狗中搜索相关文章:基于FPGA的二-十进制转码器设计

当前位置:

当前位置: