多节点大容量FPGA系统的远程升级方法

[09-12 18:31:58] 来源:http://www.88dzw.com EDA/PLD 阅读:8871次

文章摘要:2.2.2 ATmega64存储空间的扩展ATmega64的寻址空间为64 KB,利用ATmega64自身的寻址系统,只能访问0x0000~0xFFFF的地址空间。显然,这对于存储和加载大容量FPGA的配置数据是远远不够的。以Xilinx公司的Spartan3系列FPGA为例,其配置数据所需的存储空间如表2所列。表2 Spartan3系列FPGA配置文件大小以XC3S4000型FPGA为例,它的配置文件所需的存储空间约为1.35 MB,已远远超出了ATmega64单片机的寻址空间。因此,为了能够利用ATmega64单片机来实现对FPGA配置数据的读写,必须对其寻址空间进行扩展。扩展的硬件连

多节点大容量FPGA系统的远程升级方法,标签:eda技术,eda技术实用教程,http://www.88dzw.com2.2.2 ATmega64存储空间的扩展

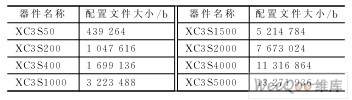

ATmega64的寻址空间为64 KB,利用ATmega64自身的寻址系统,只能访问0x0000~0xFFFF的地址空间。显然,这对于存储和加载大容量FPGA的配置数据是远远不够的。以Xilinx公司的Spartan3系列FPGA为例,其配置数据所需的存储空间如表2所列。

表2 Spartan3系列FPGA配置文件大小

以XC3S4000型FPGA为例,它的配置文件所需的存储空间约为1.35 MB,已远远超出了ATmega64单片机的寻址空间。因此,为了能够利用ATmega64单片机来实现对FPGA配置数据的读写,必须对其寻址空间进行扩展。扩展的硬件连接框图如图2中的单片机与Flash的连接部分所示。

本设计中是使用通用I/O来扩展ATmega64单片机的寻址空间的。ATmega64单片机的总寻址空间为64 KB,但片内4 KB的SRAM及各种寄存器占用了前面的部分寻址空间,故其片外存储器寻址空间是0x1100~0xFFFF。因此将Flash的低15位地址直接接到ATmega64单片机的低15位地址总线上,其余6位高位地址用单片机的通用I/O进行选择。寻址时单片机的专用地址口只输出0x8000~0xFFFF的地址数据,与通用I/O输出的地址组合后给出Flash的读写地址。

通过以上对ATmega64单片机寻址空间的扩展方法,可以实现ATmega64单片机对合适的Flash存储器的寻址操作,从而解决了大容量FPGA配置数据的存储和读取问题。

2.2.3 用ATmega64实现FPGA的SELECTMAP加载

Xilinx公司的Spartan3系列FPGA加载方式分为5种: Master Serial、Slave Serial、Master Parallel、Slave Parallel、JTAG。

按照FPGA是否控制加载过程,加载方式可分为Master方式和Slave方式;按照加载数据时的数据位宽,可分为Serial方式和Parallel方式。用于加载的引脚主要有: PROG_B,CCLK,RDWR_B,DONE,INIT_B,CS_B,BUSY,D[0~7],M[0~2],HSWAP和JTAG接口(TDI、TMS、TCK、TDO)。加载过程大体分为3个步骤: 配置的建立、配置数据的加载和加载完成。

SELECTMAP即Slave Parallel方式,是由外部控制器控制FPGA的加载过程,并以8位数据的形式向FPGA写入加载数据的加载方法。图2中FPGA与ATmega64的连接部分为ATmega64单片机采用SELECTMAP方式对FPGA进行加载的硬件连接框图,具体实现过程如下:

ATmega64通过将FPGA的PROG_B、CS_B和RDWR_B引脚置低来开启加载过程,FPGA在PROG_B置低后开始清除内部配置RAM,并将INIT_B脚置低。PROG_B重新置1后,在INIT_B由低变高的上升沿,FPGA采样M[0~2]引脚获取配置方式信息。ATmega64监视FPGA的INIT_B脚,当INIT_B脚由低变高时,说明FPGA已经完成了内部配置RAM的清除工作,并准备好接收配置数据。在ATmega64给出的CCLK配置时钟的上升沿,配置数据D[0~7]写入配置RAM。当FPGA接收完所有的配置数据后,DONE引脚被FPGA置为高电平。ATmega64可以通过监视DONE引脚来判断FPGA是否加载完成。对于Spartan3系列的FPGA,如果配置FPGA的CCLK的频率高于50 MHz,则外部控制器还需要监视FPGA的BUSY引脚。当BUSY脚为高时,说明FPGA还未完成上一个配置数据的处理,此时外部控制器需要继续保持上一个配置数据在D[0~7]引脚,直至BUSY引脚回到低电平。对于本设计的应用,ATmega64给出的配置时钟频率远低于50 MHz,不必考虑BUSY引脚的控制作用。

3 软件设计

3.1 主控计算机的软件设计

主控制计算机的软件运行状态应该分为两种: 一是平时的查询控制状态,用来查询和控制系统中各个节点的工作状态;二是系统的升级状态,用来执行对各个子节点的升级控制。如图4所示,这两种状态是可以相互转换的。

《多节点大容量FPGA系统的远程升级方法》相关文章

- › 多节点大容量FPGA系统的远程升级方法

- 在百度中搜索相关文章:多节点大容量FPGA系统的远程升级方法

- 在谷歌中搜索相关文章:多节点大容量FPGA系统的远程升级方法

- 在soso中搜索相关文章:多节点大容量FPGA系统的远程升级方法

- 在搜狗中搜索相关文章:多节点大容量FPGA系统的远程升级方法

当前位置:

当前位置: