FPGA和ARM的Profibus-DP主站通信平台设计

[09-12 18:31:07] 来源:http://www.88dzw.com EDA/PLD 阅读:8522次

文章摘要:2.2 ARM控制器部分程序设计ARM控制器程序对应于Profibus通信协议数据链路层之上的DDLM直接数据链路映射程序、主站通信状态机、应用层数据接口及应用层。本设计对Profibus-DP协议按层次封装为函数,层层调用。2.2.1 Slave_Handler状态机Slave_Handler状态机功能块负责实现主从通信功能,根据从站状态做出相应处理,有固定的处理次序,每次调用Slave_Handler状态机产生一个DDLM请求,从而控制从站进入相应的通信状态。Slave_Handler状态转换图如图2所示。2.2.2 Scheduler和FDL_Controller状态机Scheduler

FPGA和ARM的Profibus-DP主站通信平台设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com

2.2 ARM控制器部分程序设计

ARM控制器程序对应于Profibus通信协议数据链路层之上的DDLM直接数据链路映射程序、主站通信状态机、应用层数据接口及应用层。

本设计对Profibus-DP协议按层次封装为函数,层层调用。

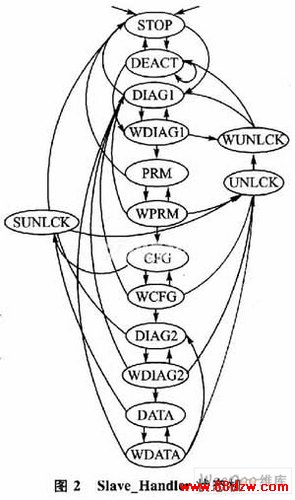

2.2.1 Slave_Handler状态机

Slave_Handler状态机功能块负责实现主从通信功能,根据从站状态做出相应处理,有固定的处理次序,每次调用Slave_Handler状态机产生一个DDLM请求,从而控制从站进入相应的通信状态。Slave_Handler状态转换图如图2所示。

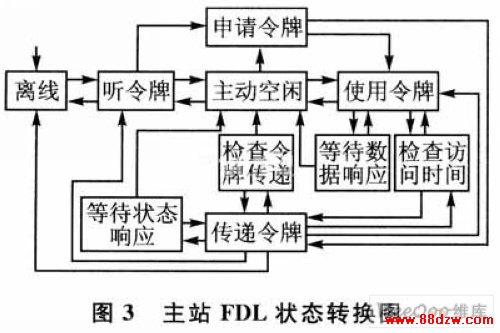

2.2.2 Scheduler和FDL_Controller状态机

Scheduler状态机功能块负责实现对Slave_Handler状态机的控制。它向Slave_Handler状态机发送从站轮询控制信号,控制其逐步与从站建立数据交换关系。

FDL_Controller状态机由10个FDL状态组成并在这些状态间转换,如图3所示。

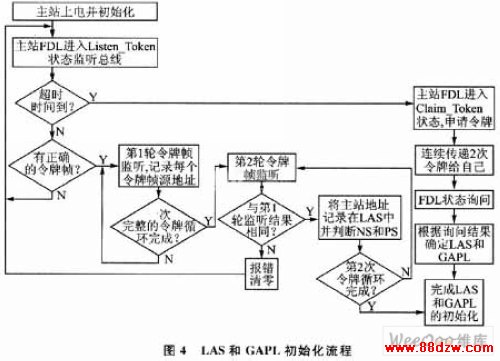

逻辑令牌环的建立主要工作是对LAS和GAPL的初始化。LAS和GAPL的具体初始化流程如图4所示。

LAS的形成标志着逻辑令牌环初始化的完成。接下来就是逻辑令牌环运转的维护阶段,令牌将按照LAS进行循环传递,得到令牌的主站有权进行对其所属从站的轮询。传递过程中主站将以固定的时间间隔,通过Request FDLStatus主动帧来询问自己GAP范围内的所有地址,并根据询问结果修改LAS和GAPL。在主站活动表生成之后,前驱站询问ReqtJest FDL Starus,主站回复准备进入逻辑令牌环,并从Listen_Token状态进入Active_Idle状态(主站的前驱站会修改自己的GAP和LAS,并把该主站作为自己的后继站)。主站在Active_Idle状态*总线,能够对寻址自己的主动帧作应答,但没有发起总线活动的权力,直到前驱站传送令牌给它,它保留令牌并进入Use_Token状态,在此状态下驱动Scheduler状态机工作。主站持有令牌后,首先计算上次令牌获得时刻到本次令牌获得时刻经过的时间(即实际轮转时间tRR),并与用户设定的目标轮转时间tTR比较,如果tRR小于tTR,则主站开始处理传输任务。首先处理高优先级传输服务,所有高优先级服务处理完毕后处理低优先级服务。在这个过程中,每一个完整的报文循环之后,主站就重新计算tTR—tTH。若结果小于0,主站进入PassToken状态,将令牌传递给后继站,未完成的任务留到下一次令牌持有的时候再执行。所有传输服务都完成后,不管是否有时间剩余,主站都交出令牌。如果主站接到令牌时发现tTR—tTH<O,则只发送一个高优先级报文,完成后交出令牌。主站在令牌传递成功后,进入Active_Idle状态,直到再次获得令牌。

3 系统工作过程

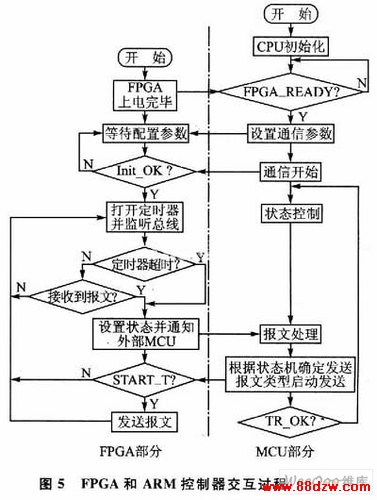

系统工作过程主要是ARM控制器和FPGA的通信交互过程,如图5所示。从系统安全性上考虑,FPGA和ARM建立通信必须有双方的确认信号,虽然Altera Cyclone系列FP-GA从上电到稳定之前引脚没有输出,从系统安全性角度考虑还是不够的。

《FPGA和ARM的Profibus-DP主站通信平台设计》相关文章

- › 高性能FPGA中的高速SERDES接口

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › FPGA在平板显示器中的应用

- › FPGA与DS18B20型温度传感器通信的实现

- 在百度中搜索相关文章:FPGA和ARM的Profibus-DP主站通信平台设计

- 在谷歌中搜索相关文章:FPGA和ARM的Profibus-DP主站通信平台设计

- 在soso中搜索相关文章:FPGA和ARM的Profibus-DP主站通信平台设计

- 在搜狗中搜索相关文章:FPGA和ARM的Profibus-DP主站通信平台设计

当前位置:

当前位置: