基于FPGA的电网实时数据采集与控制

[09-12 18:31:00] 来源:http://www.88dzw.com EDA/PLD 阅读:8819次

文章摘要:2.2 数字锁相倍频的FPGA实现输入信号经整形后也可转换为与基波信号同频率的方波,然后对方波信号进行二分频。二分频的目的有两个,一是作为控制信号来实现周期测量;二是可以消除输入波形不对称的影响,提高测量周期的精度。将二分频后的方波信号一路送K分频器I的控制端,另一路反相后接K分频器Ⅱ的控制端,以使两路K分频器在输入信号相邻两个周期内交替处于分频、清零状态。这样,两路轮流工作就可避免使用单路计数器连续计数时由于数据保持和清零过程所造成的测量误差和相位延迟问题。K分频器在每次工作前,其输出为0电平,这样可以保证计数器的输入方波与其计数周期同步,防止计数器输入方波与计数周期的随机性带来的计数误差

基于FPGA的电网实时数据采集与控制,标签:eda技术,eda技术实用教程,http://www.88dzw.com2.2 数字锁相倍频的FPGA实现

输入信号经整形后也可转换为与基波信号同频率的方波,然后对方波信号进行二分频。二分频的目的有两个,一是作为控制信号来实现周期测量;二是可以消除输入波形不对称的影响,提高测量周期的精度。将二分频后的方波信号一路送K分频器I的控制端,另一路反相后接K分频器Ⅱ的控制端,以使两路K分频器在输入信号相邻两个周期内交替处于分频、清零状态。这样,两路轮流工作就可避免使用单路计数器连续计数时由于数据保持和清零过程所造成的测量误差和相位延迟问题。K分频器在每次工作前,其输出为0电平,这样可以保证计数器的输入方波与其计数周期同步,防止计数器输入方波与计数周期的随机性带来的计数误差,从而提高测量精度。本系统中,K取128。

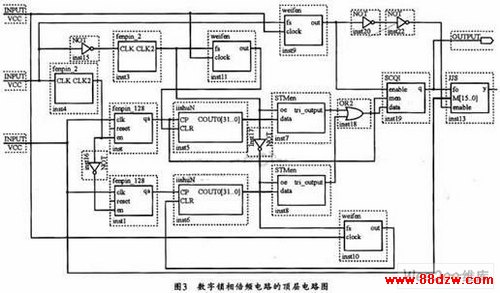

计数器的计数值N在被测周期结束后将立刻送锁存器锁存,并作为可编程分频器的分频系数N。由于采用两路计数器轮流工作方式,因此,锁存器要有选择地对每路计数器的计数结果进行锁存。考虑到要尽可能地减小相位滞后,在每个周期结束后,锁存器应在最短的时间内将数据锁存。这就要求锁存器在锁存脉冲到来前,先选择好被锁存的计数器,保证每个周期计数值的可靠锁存。锁存信号由输入方波信号经微分电路产生,这种设计使可编程分频器在每个周期的开始时刻,总是以新的数据、新的起点开始分频。两路计数器在计数工作前要先清零,使计数器的计数值准确的反映输入信号的周期。清零工作必须在计数结果锁存后的下一次计数开始前完成。数字锁相倍频的顶层电路如图3所示。

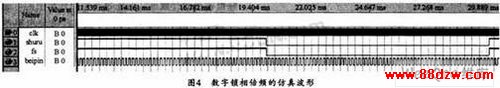

在FPGA软件QuartusII7.2开发平台上完成硬件设计后即可进行仿真,其仿真波形如图4所示。其中,标准时钟clk的频率为10 MHz;shuru:为倍频的输入信号,shuru频率设置为50 Hz,倍频系数为128;beipin:表示倍频电路的输出信号。从仿真中可以看到,本设计可以达到128倍频的效果。

3 A/D采集控制

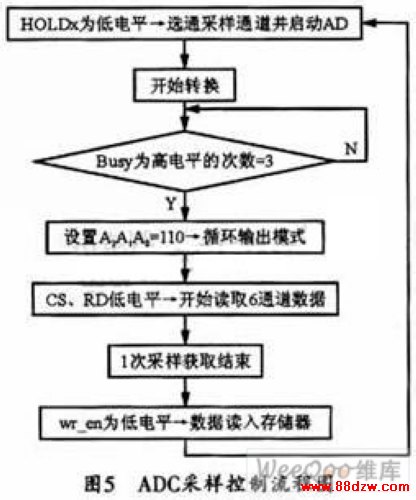

由于本设计要同时采集电网的三相电压和电流,所以,应把采样倍频信号接至HOLDA、HOLDB、HOLDC,以同时保持六路输入信号,读出模式设置为循环模式。

由ADS7864的时序图可以得到如图5所示的ADC控制器的软件控制流程。以便在QuartusII开发平台上利用VHDL语言进行软件编程。

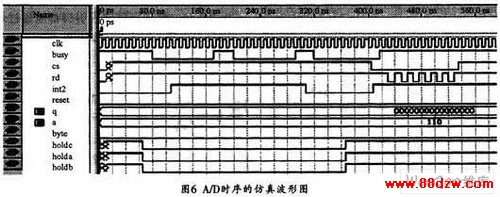

通过ADS7864的工作状态控制模块可根据ADS7864的转换时序图,用VHDL编写FPGA控制ADS7864的转换程序,并可采用双进程有限状态机的方法来在Quartus II 7.2内对A/D控制模块进行时序仿真,其仿真波形如图6所示。仿真结果表明,该模块的设计完全符合要求。

4 结束语

本文给出了基于FPGA的电网实时数据采集系统的设计方法。该方法采用FPGA作为数据采集系统的控制核心。并充分利用了高速模数转换芯片ADC和可编程逻辑控制器件FPGA,最终通过硬件描述语言VHDL实现了A/D的控制和数字锁相倍频电路。该电路具有良好的可移植性和可扩展性,便于调试和修改,在电网的实时数据采集方面有较好的应用前景。(葛远香,胡开明 东华理工大学 信息与电子工程学院,江西 抚州)

《基于FPGA的电网实时数据采集与控制》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的电网实时数据采集与控制

- 在谷歌中搜索相关文章:基于FPGA的电网实时数据采集与控制

- 在soso中搜索相关文章:基于FPGA的电网实时数据采集与控制

- 在搜狗中搜索相关文章:基于FPGA的电网实时数据采集与控制

当前位置:

当前位置: