基于VHDL的99小时定时器设计及实现

[09-12 18:30:42] 来源:http://www.88dzw.com EDA/PLD 阅读:8713次

文章摘要:(2)DISP模块DISP模块主要用于译码,可定义七段数码管显示的数字。其源程序如下:4 系统仿真及结果图6所示是对AAA控制/定时模块的仿真结果。由此结果可见,当setw置“1”时,statea位选从0到5循环,分别代表六个数码管的位置。当start置“1”时,q5-q0进行借位减法。q5、q4表示小时,最高可到99小时;q3、q2表示分钟,最高59分钟;q1、q0表示秒,最高为59秒。5 结束语本设计从总体要求出发,采用模块化设计方法,实现了长达99小时的定时设计。同时采用QuartusⅡ4.0仿真环境进行了仿真。结果证明,本系统可以实现理想的定时操作而且设计体现了人性化,具有较强的实际

基于VHDL的99小时定时器设计及实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com

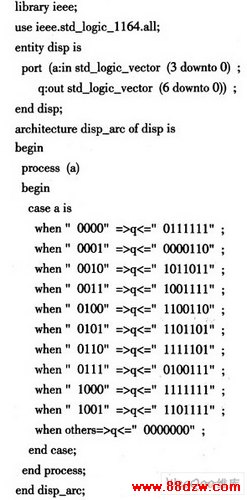

(2)DISP模块

DISP模块主要用于译码,可定义七段数码管显示的数字。其源程序如下:

4 系统仿真及结果

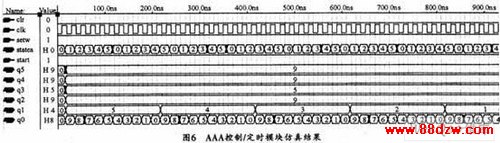

图6所示是对AAA控制/定时模块的仿真结果。由此结果可见,当setw置“1”时,statea位选从0到5循环,分别代表六个数码管的位置。当start置“1”时,q5-q0进行借位减法。q5、q4表示小时,最高可到99小时;q3、q2表示分钟,最高59分钟;q1、q0表示秒,最高为59秒。

5 结束语

本设计从总体要求出发,采用模块化设计方法,实现了长达99小时的定时设计。同时采用QuartusⅡ4.0仿真环境进行了仿真。结果证明,本系统可以实现理想的定时操作而且设计体现了人性化,具有较强的实际应用价值。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

- 上一篇:基于CPLD的激光驱动电源的设计

《基于VHDL的99小时定时器设计及实现》相关文章

- › 基于VHDL 的矩阵键盘及显示电路设计

- › 基于VHDL的可变速彩灯控制器的设计

- › 基于VHDL的图像传感器TCDl206的驱动设计

- › 基于VHDL的99小时定时器设计及实现

- › 基于VHDL语言的按键消抖电路设计及仿真

- › 基于VHDL的I2C总线控制核设计

- 在百度中搜索相关文章:基于VHDL的99小时定时器设计及实现

- 在谷歌中搜索相关文章:基于VHDL的99小时定时器设计及实现

- 在soso中搜索相关文章:基于VHDL的99小时定时器设计及实现

- 在搜狗中搜索相关文章:基于VHDL的99小时定时器设计及实现

分类导航

最新更新

当前位置:

当前位置: