FPGA的多路可控脉冲延迟系统

[09-12 18:30:35] 来源:http://www.88dzw.com EDA/PLD 阅读:8588次

文章摘要:图3 多路延迟线结构框图4 系统仿真下面给出了核心部分的RTL图及QuartusII时序仿真波形。PLL模块的RTL图如图4所示。计数模块2的RTL图如图5所示。该模块的输入clk应连接到频率为100 MHz的时钟信号,作为计数脉冲。 en是使能信号, 应连接到经过计数模块1分频后得到的1 kHz的时钟信号上。假设en信号到来,该信号为高电平时,计数器temp开始计数,到达设定的计数时间后输出高电平,否则为低电平。经过计数模块2后系统完成粗延迟,此时延迟分辨率为10 ns级。图4 PLL模块RTL图图5 计数模块2的RTL图PLL模块实现倍频的功能。其中,输入clk0应连接频率为50

FPGA的多路可控脉冲延迟系统,标签:eda技术,eda技术实用教程,http://www.88dzw.com图3 多路延迟线结构框图

4 系统仿真

下面给出了核心部分的RTL图及QuartusII时序仿真波形。PLL模块的RTL图如图4所示。

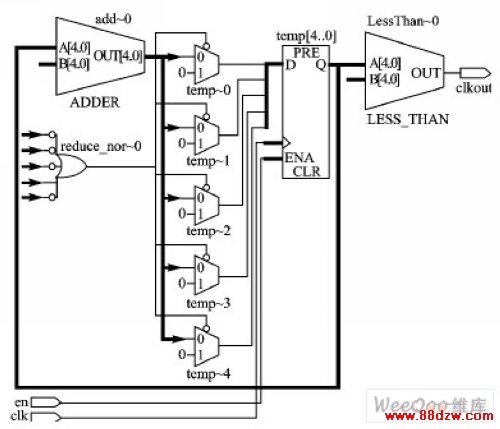

计数模块2的RTL图如图5所示。该模块的输入clk应连接到频率为100 MHz的时钟信号,作为计数脉冲。 en是使能信号, 应连接到经过计数模块1分频后得到的1 kHz的时钟信号上。假设en信号到来,该信号为高电平时,计数器temp开始计数,到达设定的计数时间后输出高电平,否则为低电平。经过计数模块2后系统完成粗延迟,此时延迟分辨率为10 ns级。

图4 PLL模块RTL图

图5 计数模块2的RTL图

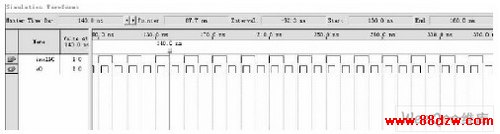

PLL模块实现倍频的功能。其中,输入clk0应连接频率为50 MHz的时钟信号。输出信号c0为100 MHz,分别送给计数模块1和2实现分频和计数脉冲的作用。其仿真波形如图6所示。

图6 PLL模块仿真波形

计数模块1和2的延迟时间均可由单片机动态写入,本方针波形写入的延迟时间为300 ns。延迟后的波形如图7所示。

结语

本设计不同于现有的延迟电路,它将数字方法图7延迟后计数模块2输出波形和模拟方法相结合,对多路连续脉冲信号进行大范围高分辨率的动态延迟,将分辨率提高到了0.15 ns级。而且,本系统用Flash FPGA替代现有系统的SRAM FPGA,从而大大提高了系统集成度,降低了成本。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《FPGA的多路可控脉冲延迟系统》相关文章

- › 高性能FPGA中的高速SERDES接口

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › FPGA在平板显示器中的应用

- › FPGA与DS18B20型温度传感器通信的实现

- 在百度中搜索相关文章:FPGA的多路可控脉冲延迟系统

- 在谷歌中搜索相关文章:FPGA的多路可控脉冲延迟系统

- 在soso中搜索相关文章:FPGA的多路可控脉冲延迟系统

- 在搜狗中搜索相关文章:FPGA的多路可控脉冲延迟系统

分类导航

最新更新

当前位置:

当前位置: