65nm FPGA���ģ����վΪ�����ĸ߶�Ӧ����

[09-12 18:30:24] ��Դ��http://www.88dzw.com EDA/PLD �Ķ���8826��

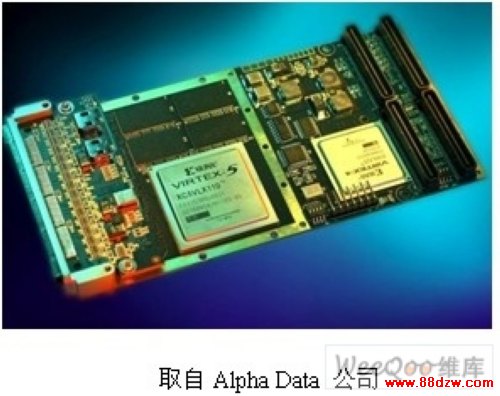

����ժҪ���ڴ�ͳ����վ��Ƕ��ʽ�źŴ���ϵͳ�У����FPGA���źŴ���������Ҫͨ�������û�ר�û����ṹ�������߽ṹ�����������ƣ��������������ϵͳ����Ҫ����ר��ϵͳ���������㻥����ͨ����Ҫ����ˣ����ڴ��н�����������Serial RapidIO��PCI Express��GEΪ������Ƕ��ʽ����������������վ�����ܴ���ϵͳ�������ڶ�ģ��վ��ϵͳ����ƽ̨����λ�õ�FPGA����Ҫֱ����ٴ��л���������Virtex 5�����õ�ȫ�� RocketIO GTP ǧ��λ�������շ�����ƺ�SelectIO����I/O����ʵ�������˴��б������в��б��������Žӣ�֧�ֲ�����Χ����100Mbps �� 3.75G

65nm FPGA���ģ����վΪ�����ĸ߶�Ӧ����,��ǩ��eda����,eda����ʵ�ý̳�,http://www.88dzw.com�����ڴ�ͳ����վ��Ƕ��ʽ�źŴ���ϵͳ�У����FPGA���źŴ���������Ҫͨ�������û�ר�û����ṹ�������߽ṹ�����������ƣ��������������ϵͳ����Ҫ����ר��ϵͳ���������㻥����ͨ����Ҫ����ˣ����ڴ��н�����������Serial RapidIO��PCI Express��GEΪ������Ƕ��ʽ����������������վ�����ܴ���ϵͳ�������ڶ�ģ��վ��ϵͳ����ƽ̨����λ�õ�FPGA����Ҫֱ����ٴ��л���������

����Virtex 5�����õ�ȫ�� RocketIO GTP ǧ��λ�������շ�����ƺ�SelectIO����I/O����ʵ�������˴��б������в��б��������Žӣ�֧�ֲ�����Χ����100Mbps �� 3.75Gbps֮������г������л����ӿڱ�Э�鲢���ڵ��� FPGA ��ʵ�ֶ��������Э�飨��sRIO��PCIe��FE/GE��FC��SAS��SATA�ȣ���RocketIO GTP�Ŀɵ�������Ԥ���غͽ��վ��⼼����������������40�� �ı��壬�ڶ���ͨ����ʵ�ֿɿ��Ľ��ա�

����Virtex 5����Ƕ��ʽPCIeģ�齫���ֹ��ܼ��ɵ�����65nm FPGA�ķ�ʽ��ʵ�֡�Virtex-5 FPGAƽ̨������ǿ��PCI Express�˵�ģ�飬����ʵ�ִ����㡢������·��������㹦�ܣ�֧�� 1��2��4 �� 8ͨ����

����Xilinx�ڶ�ӲIP����IP���бȽ�֮����Virtex 5ϵ���в�����Ƕ�������û���Ч��ʹ���ʺͽ���ϵͳ���ĵ�ӲIP�ķ�ʽ��ʵ��GE��PCIe�ȴ��л������������8ģʽ��PCIeӲ�˿��Ա���������FPGA��������ʽʵ�ֵĽ�������1.5W�Ĺ��ġ�

����Xilinx 65nm ƽ̨FPGA�����������IEEE 802.3����Ƕ��ʽ10/100/1000 Mbps��̫��MACģ�飺����ʽӲIPΪÿ����̫��MAC�ͷŴ�Լ1800������Ԫ�����ṩ�Ŀɱ��PHY�ӿ�ͬʱ֧�ֱ���MII/GMII��ʹ��RocketIO�շ���ʱ��SGMII�ӿڣ���ʹ��RocketIO�շ���ʱ������ʵ��1000 Base-X�ĵ�оƬ����������㷺Ӧ����AMC��ATCA��MicroTCA������ϵͳ�ṹ���������Ѿ�ͨ��UNH������֤�ļ����Ժͻ�������������˼�����ϵͳ����ƺ���֤��������

����Xilinx��Virtex 5ϵ�о��е���б���Ͷ����IJ��ʱ�ӽṹ�����Դﵽ550MHz�Ĺ���Ƶ�ʣ��ټ��ϸ�������ʱ�ӹ����ܵ���������� PLL ��DCM������ʱ�ӹ���������ʹ�ø������ڱ�֤��ȥSkewʵ�ֵ�ʱ�Ӷ�����ǰ����ͬʱȷ���˸߾��ȺͿ�������ԣ�����������ʱ��ϵͳ�����ܡ�

����Xilinx����65nm���յ�100Mbps�C3.75Gbps�շ���������ʽ�ӿ�ģ���ͨ��Ԥ��֤PCI Express����ģ��̫��ģ�鼰����IP�������������ɿ������㴴���弶�����弶��ϵͳ���Ļ�����Ҫ��Ҳ������һ��ͨ�š��źŴ�����ͼ�Ρ��洢�����罻����I/O�����ϵ���Ҫ�����һ�����Ʒ��ս�����ͣ���ʡ�������ڵ�ASSP��ASIC�е�Ͷ�ʡ�

���������� ���ͳɱ�

����Xilinxͨ����Virtex-5ϵ�в����¹��ա��¼������·�װ�ʹ�������ӲIP�ȷ�ʽ��ʹ�ù���ʦ��ʹ��65nm����FPGA������ƣ����Դ��������Ʒ��յ�ͬʱ����������ͬʱ����ϵͳ���ܣ�ʵ�����ܺ��ĵ���Ѿ��⣬����������ٶȡ������а���������ExpressFabric ��������������30%��ͬʱʹ��̬���Ľ���35%������ 65nm ��դ�������㼼��������©����Ϊ���ľ�̬���ģ������µ�RocketIO GTP�շ�����ʹ���ı���һ����������77%����С��ɢ��ϵͳ��һ������ϵͳ���ģ�Ƕ��ʽ Block RAM �ͷֲ�ʽ RAM/FIFO�����˶��ⲿRAM������ChipSync ��·���Խ�ʱ�ӵ������������У��Ӷ���֤�洢���ӿڵĿɿ��ԣ�SelectIO ��·�������֧�ָ���Ƭ�� I/O�ӿڱ���DSP48E slices ΪǶ��ʽ�˷����ṩ�˿�ѡ�ļӷ������ۼ�����RocketIO GTP �շ����ṩ����ʽ���� I/O ���ܺ�ҵ����͵Ĺ��ģ�PCI Express �˵�ģ��������ں� RocketIO GTP �շ���һ��ʹ�ã��Ա��ṩ���ڼ��ݵ� PCIe ���ӹ��ܣ�10/100/1000 ��̫�� MAC ģ��� RocketIO GTP �շ���һ��ʹ�ã��ṩ����ʽ��̫�����ӹ����������ֻ���65nm�������������ƣ������ϵͳ�ۺϳɱ�������ʵ��x8ģʽ��PCI Express��ʹ��Xilinx��Virtex-5 FPGA���Ա��������̵���ͬ����������Լ��10,000��LUT��

��65nm FPGA���ģ����վΪ�����ĸ߶�Ӧ�������������

- › ��FPGA���65nmоƬ�������

- › 65nm FPGA���ģ����վΪ�����ĸ߶�Ӧ����

- › ����FPGA���65nmоƬ�������

- �ڰٶ�������������£�65nm FPGA���ģ����վΪ�����ĸ߶�Ӧ����

- �ڹȸ�������������£�65nm FPGA���ģ����վΪ�����ĸ߶�Ӧ����

- ��soso������������£�65nm FPGA���ģ����վΪ�����ĸ߶�Ӧ����

- ���ѹ�������������£�65nm FPGA���ģ����վΪ�����ĸ߶�Ӧ����

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

- �� ����AVR��CPLD�ĸ������ݲɼ�ϵͳ

- �� ����FPGA���ŵ������ջ�

- �� ����FPGA��SMT387��SAR���ݲɼ���洢ϵͳ

- �� ����FPGA�ĺ����ܼ��ȹ�����в���ϵͳ

- �� FPGA ��Ƶ��еĹ�������

- �� ����FPGA��ջ�ռ���������о������

- �� ����FPGA�����ຯ���źŷ��������

- �� ����FPGA�Ŀ������ֽ��ջ�����������±�Ƶ

- �� Xilinx Spartan-3AN������Ϸ�����ܽ������

- �� ״̬����ë�̡��IJ�������������

- �� ����FPGA�Ŀɸ���ͨ�Žӿ����

- �� ����ģ�黯��Ʒ���ʵ��FPGA��̬�����ع�

- �� ���H.264���Ŀ����˶������㷨 DCS�㷨

- �� ������˹�Ƴ�����PSoC�Ŀɱ�̵�����ͨѶ��

- �� FPGA�����շ������ԭ��

- �� ���˱���������TLM����֤

- �� ��PSoC Expressʵʩ������PSoCӦ�ÿ���

- �� ����FPGAЭ��������������ϵͳ����

- �� һ��ͨ��Makefile�ı�д

- �� FPGA�Ĺ��ĸ������������о�

��ǰλ�ã�

��ǰλ�ã�