基于SCA规范下FPGA的硬件抽象层设计

[09-12 18:29:48] 来源:http://www.88dzw.com EDA/PLD 阅读:8776次

文章摘要:本设计中的FPGA采用Xilinx公司Virtex 5系列的2200万门器件XC5VLX220-1FF1760I以及500万门器件XC5VSX95T-lFF1136I。DSP选用TI公司的TMS320C6416T,该DSP具有的丰富的集成外设,可适应各种不同的应用需求。通用FLASH采用Spansion公司的S29GL512N10TAI高密度NOR型FLASH。S9GL512N的容量高达512Mbit,可以存储多个版本的DSP和FPGA程序。NOR型FLASH的读操作时序和EEPROM相同,读/写操作最短周期为100ns,可以直接用于DSP的BOOT引导。TMS320C6416T与CPLD配合

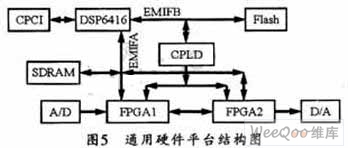

基于SCA规范下FPGA的硬件抽象层设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com本设计中的FPGA采用Xilinx公司Virtex 5系列的2200万门器件XC5VLX220-1FF1760I以及500万门器件XC5VSX95T-lFF1136I。DSP选用TI公司的TMS320C6416T,该DSP具有的丰富的集成外设,可适应各种不同的应用需求。通用FLASH采用Spansion公司的S29GL512N10TAI高密度NOR型FLASH。S9GL512N的容量高达512Mbit,可以存储多个版本的DSP和FPGA程序。NOR型FLASH的读操作时序和EEPROM相同,读/写操作最短周期为100ns,可以直接用于DSP的BOOT引导。TMS320C6416T与CPLD配合,可以控制FPGA配置文件的下载过程。FPGA芯片通过高速并行接口可与AD和DA直接相连,以进行高速的数字处理。DSP芯片可通过EMIFA(外部存储器接口)接口与FPGA进行通信。

在实际应用中,平台需以多模式的方式工作,并应根据需要实时更新功能程序。因此,用户可在FLASH芯片中划分区域,以将多种功能程序分别存储在不同区域,并确定区域首地址。系统上电复位后,DSP和FLASH芯片先完成初始化,之后DSP会按照默认方式访问默认首地址并加载默认DSP和FPGA功能程序,以便系统工作在默认模式下;当需要更新模式时,主控设备先发送指令,DSP检测到指令后,DSP便按照指令要求查到对应首地址,并从新功能的首地址开始为DSP和FPGA加载新的功能程序,系统即工作在新模式下。如此便可在同一个硬件平台上,通过动态调用不同的软件程序来实现多功能、多模式的工作。

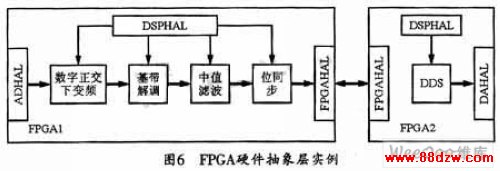

利用此硬件平台还可实现MSK数字调制解调功能。FPGA的硬件抽象层的实现可将FPGA与外部接口在FPGA内,用一个专用的小模块来实现对外交互,并在这个特定模块里定义好HC与外部交互的接口形式(如数据总线,相关的时钟信号、控制信号等)。然后根据功能需要在FPGA内为AD、DA、DSP、CPLD以及互连的FPGA抽象出独立的标准通信接口模块ADHAL、DAHAL、DSPHAL、CPLDHAL和FPGAHAL,另外,还需要设计MSK调制和解调的HC模块,其中调制部分包括DDS和数字正交上变频两个子模块。数字正交上变频可采用AD9779来实现。解调部分主要包括数字正交下变频、基带解调、中值滤波和位同步四个子模块。这些HC模块均为独立的文件,而且各个模块的参数均可配置。这样便可利用上述编制好的文件来实现MSK调制解调功能。事实上,只需要在一个工程中把用到的文件包含进来,并在顶层文件中实例化各个模块,同时根据实际硬件连接约束FPGA的引脚,最后通过综合实现并生成FPGA配置文件,再用DSP和CPLD来完成配置,即可实现如图6所示的FPGA内部抽象层。也可以通过主机动态配置各个模块的参数以及连接关系,以实现不同频段的调制和解调。如果要完成其它方式的数字调制解调,只需要把MSK调制和解调的HC模块替换为其他数字调制解调算法,并通过主机发送指令重新对FPGA进行配置即可。这样就可提高软件模块的可移植性、可重用和可互操作性。

4结束语

通过HAL-C提供的平台,不但可使波形应用开发者从底层硬件的细节处理中脱离出来,专注实现组件的算法功能,而且,基于FPGA硬件抽象层连接设计的软件,还具有很好的可移植性,因而能有效缩短系统开发周期,提高系统开发效率。(张晓波,窦衡 电子科技大学)

《基于SCA规范下FPGA的硬件抽象层设计》相关文章

- › 基于SCWS技术的图形化界面卡的接口与安全

- › 基于SCA规范下FPGA的硬件抽象层设计

- 在百度中搜索相关文章:基于SCA规范下FPGA的硬件抽象层设计

- 在谷歌中搜索相关文章:基于SCA规范下FPGA的硬件抽象层设计

- 在soso中搜索相关文章:基于SCA规范下FPGA的硬件抽象层设计

- 在搜狗中搜索相关文章:基于SCA规范下FPGA的硬件抽象层设计

当前位置:

当前位置: