在FPGA中实施4G无线球形检测器

[09-12 18:29:42] 来源:http://www.88dzw.com EDA/PLD 阅读:8437次

文章摘要:球形检测器(SD)的流水线架构可以在每个时钟周期中处理数据。其结果就是树的每级只需要一个PED模块。因此,对4x4 64-QAM系统而言,PED单元的总数为8,与树的级数相等。SD可以采用硬解码和软解码两种类型的解码技术。硬解码能够用贯穿树的各级的最小距离矩阵度量次序;软解码用对数似然比来代表输出的每个比特。对数似然比一般被当作优先输入值提供给信道解码器,比如turbo解码器。FPGA资源占用实施和仿真包括MIMO 802.16e宽带无线接收检测过程,但不包括软输出生成模块。目标芯片是Virtex-5 XC5VFX130T-2FF1738 FPGA。设计的时钟频率为225MHz,可用的数据率为

在FPGA中实施4G无线球形检测器,标签:eda技术,eda技术实用教程,http://www.88dzw.com球形检测器(SD)的流水线架构可以在每个时钟周期中处理数据。其结果就是树的每级只需要一个PED模块。因此,对4x4 64-QAM系统而言,PED单元的总数为8,与树的级数相等。

SD可以采用硬解码和软解码两种类型的解码技术。硬解码能够用贯穿树的各级的最小距离矩阵度量次序;软解码用对数似然比来代表输出的每个比特。对数似然比一般被当作优先输入值提供给信道解码器,比如turbo解码器。

FPGA资源占用

实施和仿真包括MIMO 802.16e宽带无线接收检测过程,但不包括软输出生成模块。目标芯片是Virtex-5 XC5VFX130T-2FF1738 FPGA。设计的时钟频率为225MHz,可用的数据率为83.965MB/s。

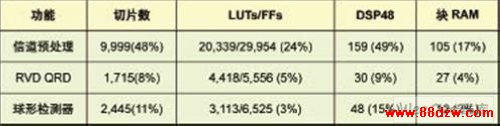

表1显示了设计中每个主要功能单元的资源占用情况。利用率(%)表示FPGA面积占XC5VFX130T器件总面积的百分比。

表1 按子系统划分的资源占用情况

System Generator和基于模型的设计

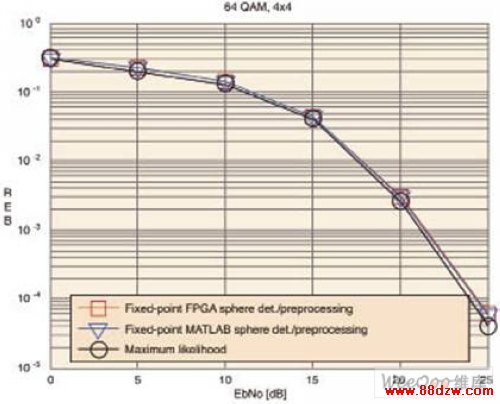

我们使用针对DSP设计流程的赛灵思System Generator实现了完整的硬判链。设计验证工作不仅使用了MATLAB/Simulink 环境的仿真语义,还有System Generator的协同仿真功能。信道矩阵参数的同相部分和正交部分从正常的分布得出,并由MATLAB交付给System Generator建模环境。我们同样使用这种仿真框架进行了比特误码率计算。图3对我们的定点硬判决设计BER曲线、浮点硬判决设计BER曲线和最佳ML参考曲线进行了比较。我们通过对赛灵思ML510开发平台进行基于以太网的硬件协仿真,开发出了该设计的硬件演示。信道矩阵参数采用赛灵思AWGN IP核发送给球形检测器。我们通过把设计嵌入到自同步BER测试器来计算BER。该仪器能够向检测器发送输入并捕获误码。

图3 4x4 64-QAM的浮点MATLAB仿真(硬判决)、System

Generator设计(硬判决)BER曲线与最大似然曲线相比

本文就采用空分复用MIMO的通信系统使用的球形检测器进行了简要介绍。我们详细探讨了球形检测器和信道矩阵预处理器的架构情况。实现预处理的方法有许多种,虽然我们的方法在计算上要复杂一点,但得出的BER性能接近最大似然。虽然我们的讨论是围绕WiMAX进行的,设计人员可以把其中的许多方法用于3G/ LTE(长期演进)无线系统。(赛灵思公司)

《在FPGA中实施4G无线球形检测器》相关文章

- › 在FPGA中实现PCI Express桥接解决方案

- › 在FPGA中实施4G无线球形检测器

- › 在FPGA中实现源同步LVDS接收正确字对齐

- › 雷达视频积累算法在FPGA上的实现

- › CVSD算法分析及其在FPGA中的实现

- › IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器

- 在百度中搜索相关文章:在FPGA中实施4G无线球形检测器

- 在谷歌中搜索相关文章:在FPGA中实施4G无线球形检测器

- 在soso中搜索相关文章:在FPGA中实施4G无线球形检测器

- 在搜狗中搜索相关文章:在FPGA中实施4G无线球形检测器

当前位置:

当前位置: