基于ARM+FPGA的重构控制器设计

[09-12 18:29:14] 来源:http://www.88dzw.com EDA/PLD 阅读:8767次

文章摘要:TRST:可选复位信号,低电平有效。Xilinx器件接受使用JTAG TAP的编程指令和测试指令。在IEEE 1149.1的标准中,用于CPLD,FPGA以及配置PROM的常见指令有:旁路(BYPASS)指令,通过用1 b长的BYPASS寄存器将TDI与TDO直接连接,绕过(即旁路)边界扫描链中的某个器件;EXTEST指令,将器件I/O引脚与内部器件电路分离,以实现器件间的连接测试,它通过器件引脚应用测试值并捕获结果;IDCODE指令,返回用于定义部件类型、制造商和版本编号的32位硬件级别的识别码;HIGHZ指令,使所有器件引脚悬置为高阻抗状态;CFG_IN/CFG_OUT指令,允许访问配置和

基于ARM+FPGA的重构控制器设计,标签:eda技术,eda技术实用教程,http://www.88dzw.comTRST:可选复位信号,低电平有效。

Xilinx器件接受使用JTAG TAP的编程指令和测试指令。在IEEE 1149.1的标准中,用于CPLD,FPGA以及配置PROM的常见指令有:旁路(BYPASS)指令,通过用1 b长的BYPASS寄存器将TDI与TDO直接连接,绕过(即旁路)边界扫描链中的某个器件;EXTEST指令,将器件I/O引脚与内部器件电路分离,以实现器件间的连接测试,它通过器件引脚应用测试值并捕获结果;IDCODE指令,返回用于定义部件类型、制造商和版本编号的32位硬件级别的识别码;HIGHZ指令,使所有器件引脚悬置为高阻抗状态;CFG_IN/CFG_OUT指令,允许访问配置和读回所用的配置总线;JSTART,当启动时钟=JTAGCLK时为启动时序提供时钟。

2.2 Tap状态机时序介绍

JTAG边界扫描测试由测试访问端口的TAP控制器管理。TMS,TRST和TCK引脚管理TAP控制器的操作,TDI和TDO位数据寄存器提供串行通道。TDI也为指令寄存器提供数据,然后为数据寄存器产生控制逻辑。对于选择寄存器、装载数据、检测和将结果移出的控制信号,由测试时钟(TCK)和测试模式(TMS)选择两个信号控制。测试复位信号(TRST,一般以低电平有效)一般作为可选的第五个端口信号。

如图2所示,所有基于JTAG的操作都必须同步于JTAG时钟信号TCK。所有测试逻辑的变化(例如指令寄存器,数据寄存器等)必须出现在TCK的上升沿或下降沿。关键时序关系是:TMS和TDI采样于TCK的上升边沿,一个新的TDO值将于TCK下降边沿后出现,因此一般情况下JTAG的时钟不会太高。

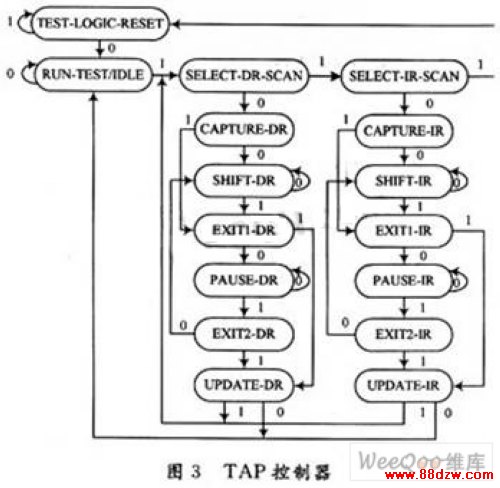

图3表示了IEEE 1149.1标准定义的TAP控制器的状态图,TAP控制器是16个状态的有限状态机,为JTAG接口提供控制逻辑。TAP状态转移如图3所示,箭头上的1或0,表示TMS在TCK上升沿的值(高电平TMS=1,低电平TMS=0),同步时钟TCK上升沿时刻TMS的状态决定状态转移过程。对于TDI端输入到器件的配置数据有两个状态变化路径:一个用于移指令到指令寄存器中,另一个用于移数据到有效的数据寄存器,该寄存器的值由当前执行的JTAG指令决定。当TAP控制器处于指令寄存器移位(SHIFT-IR)状态时,对于每一个TCK的上升沿,连接在TDI和TDO之间的指令寄存器组中的移位寄存器向串行输出方向移一位。

当TMS保持为高电平时,在TCK的上升沿TAP控制器进入到“EXIT1-IR”状态;当TMS为低电平时,TAP控制器保持在“指令寄存器移位”状态。

3重构控制器设计

3.1硬件系统组成

其主要功能是控制按照用户不同需求控制调用不同的方案配置目标可编程器件。它主要包括ARM处理器、FPGA、FLASH存储器和对外总线接口,各功能部件主要功能如下:

(1)ARM处理器选用AT91FR40162S,其主要功能是控制模拟JTAG接口的FPGA读取FLASH存储器中的重构方案,实现在系统配置;

(2)FPGA协处理器选用Xilinx公司SPARTEN3AN系列的XC3S700AN-FGG484,是基于非易失性存储的FPGA,自身带有PROM,它作为外部总线和ARM控制器之间的双端口,主要功能是模拟JTAG接口实现TAP控制器时序,完成配置方案数据的并串转换并输出至外部总线;

(3)FLASH存储器容量为32M×16 b,用于处理器的上电引导、存放多种重构配置方案。由于要求的存储容量较大,采用SPANSION公司S29GL512P(32M×16 b)的存储空间,访问速度为110 ns,可以达到25 ns快速页存取和相应的90 ns随机存取时间,FBGA封装;

(4)外部总线接口,可采用1路RS 232驱动接收器,实现和外部通信的接口;

(5)测试线TCK,TMS,TDI和TDO,是重构控制器向目标可编程器件提供所需的JTAG TAP激励,分别控制目标多个FPGA的重构配置和反馈重构信息。

《基于ARM+FPGA的重构控制器设计》相关文章

- › 基于ARM+FPGA的重构控制器设计

- › 基于ARM的FPGA加载配置实现

- › 基于ARM7+μC/OSII的数据采集系统设计

- › 基于ARM的信号发生器人机交互系统设计

- › 基于ARM嵌入式系统的ISP设计

- › 基于ARM微处理器的uC/OS的移植设计

- 在百度中搜索相关文章:基于ARM+FPGA的重构控制器设计

- 在谷歌中搜索相关文章:基于ARM+FPGA的重构控制器设计

- 在soso中搜索相关文章:基于ARM+FPGA的重构控制器设计

- 在搜狗中搜索相关文章:基于ARM+FPGA的重构控制器设计

当前位置:

当前位置: