基于CPLD器件在时间统一系统中的应用

[09-12 18:28:00] 来源:http://www.88dzw.com EDA/PLD 阅读:8574次

文章摘要:图2中,置数电路将预置好的时间置入,使得芯片内部的365进制计数器从此时刻开始计数。主时钟是频率为10MHz的晶振,作为芯片内部时序脉冲发生器的时钟信号。可编程芯片内部电路设计是本课题设计的核心。图3中,时序脉冲发生器由七级4017级联而成,由外输入时钟作为第一级的时钟。第七级产生的秒信号作为365进制计数器的时钟,该计数器组由九个十进制同步计数器74LS162组成,输出7位二进制形式的秒信号,7位分信号,6位时信号,10位天信号(分为低八位和高二位天信号两组)。输出的时间信号送至缓冲器,由时序脉冲发生器的第六级输出周期为100ms的时钟信号作为缓冲器的内部时钟,将缓冲过的时间信号以B码的格式

基于CPLD器件在时间统一系统中的应用,标签:eda技术,eda技术实用教程,http://www.88dzw.com图2中,置数电路将预置好的时间置入,使得芯片内部的365进制计数器从此时刻开始计数。主时钟是频率为10MHz的晶振,作为芯片内部时序脉冲发生器的时钟信号。可编程芯片内部电路设计是本课题设计的核心。图3中,时序脉冲发生器由七级4017级联而成,由外输入时钟作为第一级的时钟。第七级产生的秒信号作为365进制计数器的时钟,该计数器组由九个十进制同步计数器74LS162组成,输出7位二进制形式的秒信号,7位分信号,6位时信号,10位天信号(分为低八位和高二位天信号两组)。输出的时间信号送至缓冲器,由时序脉冲发生器的第六级输出周期为100ms的时钟信号作为缓冲器的内部时钟,将缓冲过的时间信号以B码的格式顺序送入并串转换电路。并串转换电路的置位信号由时序脉冲发生器第六级的Q8提供,每100ms将输入的时间信号锁存一次,时序脉冲发生器的第五级输出的周期为10ms的时钟作为并串转换的时钟,将并行数据串行输出。时序脉冲发生器通过逻辑门的控制产生了B码的三种脉冲形式:第一种是高电平为2 ms ,低电平为8ms的脉冲(代表逻辑"0");第二种是高、低电平均为5 ms的脉冲(代表逻辑"1");第三种是高电平为8 ms ,低电平为2ms的脉冲(作为位置识别标志和参考码元)。并串转换输出的串行码经过逻辑门的控制,码?1"转化为B码脉冲的第一种形式,码元"0"转化为B码脉冲的第二种形式,即将二进制的时间信号转变成为B码形式。参考码元、时间码元、位置识别标志综合在一起作为真正的B码输出。 function ImgZoom(Id)//重新设置图片大小 防止撑破表格 { var w = $(Id).width; var m = 650; if(w

3 主要单元电路设计

3.1 置数电路

根据课题要求,电路应具有置数功能。置数电路如图 4 所示,改进后的置数电路如图 5所示。

图4 置数电路

图5 改进的置数电路

将预置的天、时、分、秒在上电的同时置入各个计数器中。由于计数器74LS162是同步计数器,要求置数脉冲有效时(低电平有效)至少有一个时钟的上升沿。

计数器的时钟是由时序脉冲发生器提供的秒信号,为了保证在置数脉冲有效时存在一个时钟上升沿,对秒信号作如下改进:

输入信号clka 由时序脉冲发生器产生,输出信号clk 作为365进制计数器的时钟。输入输出波形关系如图 6所示。

图6 置数电路波形图

3.2 可编程芯片EPM7128SLC84-15内部电路

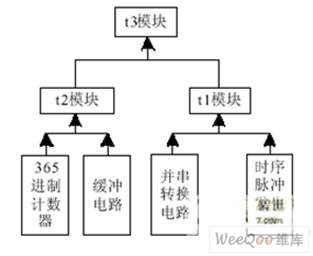

本部分采用层次结构的设计,由底层到顶层将复杂的电路模块化,最后生成一个顶层模块。图7 表示内部电路的层次结构。

图7 层次结构图

最底层的四个模块分别包含四部分较复杂的电路,将四个模块分为两组,又生成较高层的模块t1和t2,模块t1和t2最终生成最顶层的模块。采取模块化设计的优点在于可以由底层到顶层对每一个模块分别进行仿真,有利于各个模块间时序的配合。

(1)t2模块

365进制计数器

该部分电路由九个十进制同步计数器 74LS162级联而成,称为计数链,生成的模块形式如图 8所示。

- 上一篇:FPGA与CPLD的辨别和分类

《基于CPLD器件在时间统一系统中的应用》相关文章

- › 基于CPCI总线的多网口卡设计

- › 一种基于CPLD的声发射信号传输系统设计

- › 基于CPLD的臭氧电源控制系统的软硬件设计

- › 基于CPLD/FPGA的CMI编码设计与实现

- › 基于CPLD的压电生物传感器检测电路设计

- › 基于CPLD的CCD信号发生器的研究

- 在百度中搜索相关文章:基于CPLD器件在时间统一系统中的应用

- 在谷歌中搜索相关文章:基于CPLD器件在时间统一系统中的应用

- 在soso中搜索相关文章:基于CPLD器件在时间统一系统中的应用

- 在搜狗中搜索相关文章:基于CPLD器件在时间统一系统中的应用

当前位置:

当前位置: