基于FPGA的一种新型8通道数据采集系统

[09-12 18:27:44] 来源:http://www.88dzw.com EDA/PLD 阅读:8549次

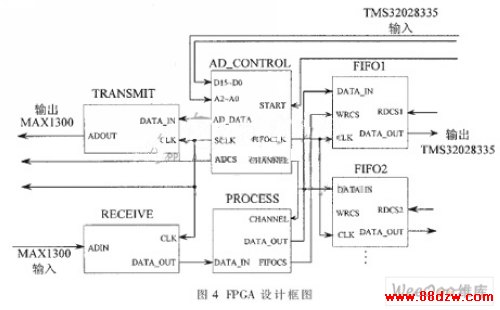

文章摘要:TMS32028335需要完成伺服系统主要的伺服算法工作,其根据算法需要,在适当时刻通过FPGA启动MAX1300,CS变低,WR变低,数据线和地址线信息写入FPGA,启动MAX1300采集数据。当采集工作完成后,对数据进行读取,CS变低,RD变低,从FPGA读取数据进行处理,完成伺服算法。2 FPGA时序控制MAX1300正常工作需要32个工作时钟,而普通MCU或DSP芯片SPI通信端口最大支持16个工作时钟,使用起来很不方便,因此实际工作中采用FPGA控制MAX1300的工作时序及数据采集,DSP读取MAX1300采集并经FPGA处理后的数据。FPGA内部时序设计如图4所示。如图4所示,F

基于FPGA的一种新型8通道数据采集系统,标签:eda技术,eda技术实用教程,http://www.88dzw.comTMS32028335需要完成伺服系统主要的伺服算法工作,其根据算法需要,在适当时刻通过FPGA启动MAX1300,CS变低,WR变低,数据线和地址线信息写入FPGA,启动MAX1300采集数据。当采集工作完成后,对数据进行读取,CS变低,RD变低,从FPGA读取数据进行处理,完成伺服算法。

2 FPGA时序控制

MAX1300正常工作需要32个工作时钟,而普通MCU或DSP芯片SPI通信端口最大支持16个工作时钟,使用起来很不方便,因此实际工作中采用FPGA控制MAX1300的工作时序及数据采集,DSP读取MAX1300采集并经FPGA处理后的数据。FPGA内部时序设计如图4所示。

如图4所示,FPGA时序设计主要由数据发送模块TRANSMIT、数据接收模块RECEIVE、数据处理模块PROCESS、A/D采集控制模块AD_CONTROL以及存储FIFO组成。

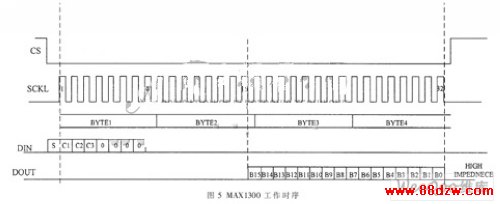

实际采集中,AD_CONTROL模块按DSP要求控制MAX1300时序工作。需要采集数据时,START信号变低后(START连接DSP的WR信号),AD_CONTROL读取TMS32028335数据线和地址线信息(地址线选择MAX1300采集通道,数据线加载MAX1300配置数据),并将相应数据AD_DATA写入TRANSMIT模块(配置MAX1300,选择采集通道)。随后ADCS信号变低,同时SCLK时钟开始工作,TRANSMIT模块在SCLK时钟作用下将数据由ADOUT引脚按位输出。在采集数据之前先对MAX1300进行配置,选择电压范围以及时钟工作模式。随后AD_CONTROL连续输出32个工作时钟,在前16个时钟选择数据采集通道,后16个时钟接收MAX1300输出数据。AD_CONTROL模块根据地址线高低电平产生通道选择信号CHANNEL,同时产生内部FIFO工作时钟FIFOCLK,控制存储FIFO的读写。

从第17个工作时钟开始,在每个时钟的下降沿MAX1300输出A/D转换后的数据。数据接收模块RECEIVE在SCLK时钟作用下对数据接收。接收机制采用通用UART设计机理,用16倍SCLK的时钟RDCLK对每位数据进行16次采样。若高电平采样次数超过10次,则认为为“1”,否则为“0”。当16位数据接收完毕时,模块将其转换为并行数据输送给数据处理模块PROCESS。

MAX1300工作时序如图5所示。

为了防止A/D数据采集过程中由于外界因素产生各种干扰(如尖峰干扰),采用类似于中值滤波的处理方法。设计中添加PROCESS模块对数据进行处理。采集数据时,每个通道数据采样10组,每组采样3次。将每一组的中值取出后求其平均值,作为此次采样数据的值。这样在一定程度上去除了外界因素对结果的影响,也为CPU进行下一步滤波减轻了负担。PROCESS模块对数据处理后,FIFOCS信号不变低,根据AD_CONTROL给出的CHANNEL信号,在FIFOCLK时钟作用下将数据写入对应的FIFO中,每路数据对应一个FIFO模块。

PROCESS模块处理后的数据存储在相应FIFO中,TMS32028335在适当时刻进行读取。读取数据时, CS和RD信号变低,FPGA根据地址线A2~A0,内部通过译码产生RDCS1、RDCS2等信号(内部译码部分图5中未标出),从相应FIFO读取相应通道的采集数据。

本文提出一种新型8通道数据采集系统,适合应用在高精度伺服控制系统中。详细介绍了A/D转换模块和CPU硬件设计电路,采用FPGA完成整个电路时序控制工作。同时,在FPGA内部设置数据预处理模块,对所采集数据进行前置处理,减轻CPU负担,加大其数据处理的能力。经实际工作测试,该设计很好地完成8通道、16位数据采集处理工作,达到系统指标要求。(电子技术应用 文 军, 何 为, 王 平, 徐 志, 王 峰, 李 罗)

- 上一篇:源码级和算法级的功耗测试与优化

《基于FPGA的一种新型8通道数据采集系统》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的一种新型8通道数据采集系统

- 在谷歌中搜索相关文章:基于FPGA的一种新型8通道数据采集系统

- 在soso中搜索相关文章:基于FPGA的一种新型8通道数据采集系统

- 在搜狗中搜索相关文章:基于FPGA的一种新型8通道数据采集系统

当前位置:

当前位置: