基于VHDL语言的按键消抖电路设计及仿真

[09-12 18:26:59] 来源:http://www.88dzw.com EDA/PLD 阅读:8395次

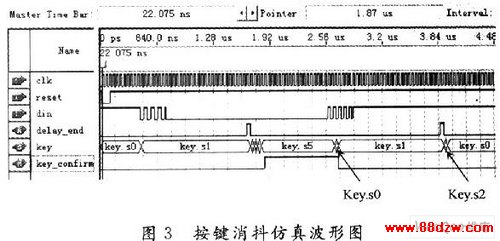

文章摘要:3 按键消抖电路的仿真分析消抖电路的仿真图如图3所示。当复位信号Reset=‘0’时,状态机Key处在S0状态,同时以CLK的时钟频率采样按键输入信号Din的状态,当CLK第一次采样到Din为低电平时,此时可能发生了按键操作,随即状态机Key进入S1消抖延时状态,当延时结束时delay_end=‘1’(延时结束信号),跟接着状态机KEY的S2,S3,S4连续三个状态对按键输入信号Din进行采样,当三个状态下采样到Din信号都是低电平,则转入S5状态,并产生按键确认信号Key_confirm=‘1’,同时在S5状态下等待按键释放,在此状态下当CLK时钟信号检测到Din为高电平时转回状态S0。因按

基于VHDL语言的按键消抖电路设计及仿真,标签:eda技术,eda技术实用教程,http://www.88dzw.com3 按键消抖电路的仿真分析

消抖电路的仿真图如图3所示。当复位信号Reset=‘0’时,状态机Key处在S0状态,同时以CLK的时钟频率采样按键输入信号Din的状态,当CLK第一次采样到Din为低电平时,此时可能发生了按键操作,随即状态机Key进入S1消抖延时状态,当延时结束时delay_end=‘1’(延时结束信号),跟接着状态机KEY的S2,S3,S4连续三个状态对按键输入信号Din进行采样,当三个状态下采样到Din信号都是低电平,则转入S5状态,并产生按键确认信号Key_confirm=‘1’,同时在S5状态下等待按键释放,在此状态下当CLK时钟信号检测到Din为高电平时转回状态S0。因按键释放瞬间也会发生抖动,所以由波形图可以看出,当按键释放瞬间由状态S5转回状态S0,在S0状态下,因按键抖动CLK时钟又检测到Din为低电平,随即转入S1进行消抖延时,经过S1的消抖延时后,按键已经稳定,Din为稳定的高电平,所以在状态S2检测到Din为高电平,则转入S0状态,到此时完成一次按键的操作,等待下一次按键操作,如果没有按键操作,即按键没按下,则一直保持在状态S0。

4 结 语

采用有限状态机方法设计按键消抖电路,再根据按键的特性设定合适的延时时间(一般10 ms)后,通过仿真分析及实验验证,能够起到很好的消抖效果,而且性能稳定,能确保每一次按键操作,产生一次按键确认,可广泛应用于可编程逻辑器件的键盘扫描设计中。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《基于VHDL语言的按键消抖电路设计及仿真》相关文章

- › 基于VHDL 的矩阵键盘及显示电路设计

- › 基于VHDL的可变速彩灯控制器的设计

- › 基于VHDL的图像传感器TCDl206的驱动设计

- › 基于VHDL的99小时定时器设计及实现

- › 基于VHDL语言的按键消抖电路设计及仿真

- › 基于VHDL的I2C总线控制核设计

- 在百度中搜索相关文章:基于VHDL语言的按键消抖电路设计及仿真

- 在谷歌中搜索相关文章:基于VHDL语言的按键消抖电路设计及仿真

- 在soso中搜索相关文章:基于VHDL语言的按键消抖电路设计及仿真

- 在搜狗中搜索相关文章:基于VHDL语言的按键消抖电路设计及仿真

分类导航

最新更新

当前位置:

当前位置: