基于ADC和FPGA脉冲信号测量设计

[09-12 18:26:37] 来源:http://www.88dzw.com EDA/PLD 阅读:8672次

文章摘要:3FPGA软件设计本系统中的时域参数测量和频域参数测量工作由FPGA担任,其输入为正交信号两路序列,输出分别为脉宽(PW)、重复周期(Pri)和频率(f)。FPGA中的数字信号处理流程如图4所示。图中,I(n)和Q(n)为两路正交信号序列;A (n)为幅度信息序列;为相位信息序列。两路正交信号I(n)和Q(n) 序列经过幅相解算后,即可得到幅度序列和相位序列。对于幅度序列,经过低通滤波和归一化,可得到规则脉冲,再按时域参数测量原理得到PW和Pri;对于相位序列,按照频率测量原理可得到频率f;然后将PW、Pri及f值存人双口RAM,再将所存数据通过模拟串口从FPGA的通用I/O口传出,经MAX2

基于ADC和FPGA脉冲信号测量设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com

3FPGA软件设计

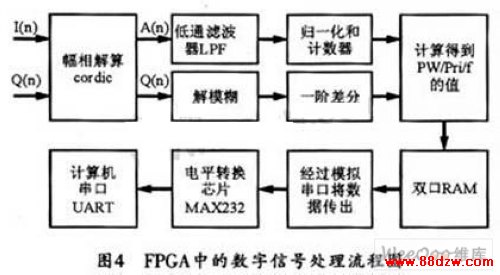

本系统中的时域参数测量和频域参数测量工作由FPGA担任,其输入为正交信号两路序列,输出分别为脉宽(PW)、重复周期(Pri)和频率(f)。FPGA中的数字信号处理流程如图4所示。

图中,I(n)和Q(n)为两路正交信号序列;A (n)为幅度信息序列;为相位信息序列。

两路正交信号I(n)和Q(n) 序列经过幅相解算后,即可得到幅度序列和相位序列。对于幅度序列,经过低通滤波和归一化,可得到规则脉冲,再按时域参数测量原理得到PW和Pri;对于相位序列,按照频率测量原理可得到频率f;然后将PW、Pri及f值存人双口RAM,再将所存数据通过模拟串口从FPGA的通用I/O口传出,经MAX232电平转换后输入到计算机串口中,最后通过上位机显示出来,以实现人机通信。

4结束语

本系统的输入信号要求为正交信号,通常可用于通信和雷达信号的后端数字信号处理。本系统采用相位差分算法来计算频率,运算简单,FPGA速度可以优化到200 M本系统利用了采样芯片和FPGA的高速性,从而实现了很高的测量精度和实时检测的目的;由于采用模拟串口进行传输,故其抗干扰性能较好。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《基于ADC和FPGA脉冲信号测量设计》相关文章

- › 基于ADC和FPGA脉冲信号测量设计

- › 基于ADuC834单片机的一氧化碳监测报警仪设计

- › 基于AD7190的Σ-Δ型ADC精密电子秤的设计

- › 基于ADS7846的电阻式触摸屏接口设计

- › 基于AD9951射频正弦波信号发生器的设计

- 在百度中搜索相关文章:基于ADC和FPGA脉冲信号测量设计

- 在谷歌中搜索相关文章:基于ADC和FPGA脉冲信号测量设计

- 在soso中搜索相关文章:基于ADC和FPGA脉冲信号测量设计

- 在搜狗中搜索相关文章:基于ADC和FPGA脉冲信号测量设计

分类导航

最新更新

当前位置:

当前位置: