基于对EPCS在线编程的FPGA可重构方法

[09-12 18:26:35] 来源:http://www.88dzw.com EDA/PLD 阅读:8886次

文章摘要:(4)为了确认擦除操作是否已操作成功,可以执行一次读状态控制命令。读状态命令也需要先打开写使能,再发送读状态命令。如果擦除过程正在进行,则DATA信号线上会返回0000 0001的数据,擦除操作完成后,DATA信号线上将返回0000 0000的数据,此时便可以进行下一步的工作。(5)当确认擦除操作完成后,就可以进行EPCS配置芯片的数据写入操作了。数据的写入需要按帧依次写入到对应的存储地址,数据存储的首地址为0000 0000。(6)所需的配置数据流发送完毕后,可发送控制命令以使CPLD器件释放对EPCS配置芯片的控制权,即置nCS、DCLK、ASDI、DATA信号线为高阻状态,并将nCONF

基于对EPCS在线编程的FPGA可重构方法,标签:eda技术,eda技术实用教程,http://www.88dzw.com(4)为了确认擦除操作是否已操作成功,可以执行一次读状态控制命令。读状态命令也需要先打开写使能,再发送读状态命令。如果擦除过程正在进行,则DATA信号线上会返回0000 0001的数据,擦除操作完成后,DATA信号线上将返回0000 0000的数据,此时便可以进行下一步的工作。

(5)当确认擦除操作完成后,就可以进行EPCS配置芯片的数据写入操作了。数据的写入需要按帧依次写入到对应的存储地址,数据存储的首地址为0000 0000。

(6)所需的配置数据流发送完毕后,可发送控制命令以使CPLD器件释放对EPCS配置芯片的控制权,即置nCS、DCLK、ASDI、DATA信号线为高阻状态,并将nCONFIG信号线由低电平置为高电平,nCE信号线置为由高电平置为低电平。一旦FPGA器件接手EPCS配置芯片的控制权,在检测到nCONFIG信号线的上升沿后,FPGA将下载EPCS配置芯片内的数据进行重新配置,此过程与系统上电时的配置过程相同。经过上述一系列的操作,便可实现一次FP-GA的重构过程。

2.4 系统设计特点

本文所述的FPGA可重构设计方案可以在系统不关电的情况下进行重构过程,这样就不会影响系统其它部分电路正在进行的工作,极大地方便了用户的实际应用。当一次用户所需的配置完成后,系统下次上电后就会自动执行最后一次所重构的工作模式,不必每次上电进行重构工作。

3 可重构设计的验证

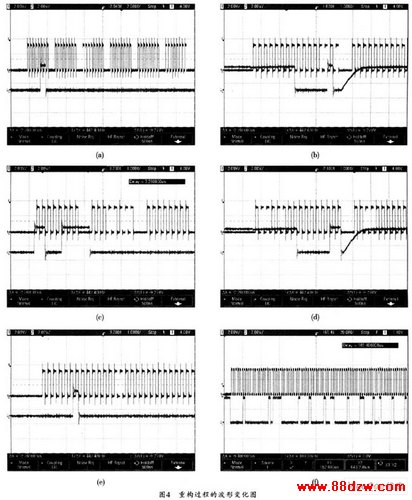

图4所示是按照本系统设计的步骤要求,在数字化仪平台上对可重构系统进行全面测试的部分重构波形变化图,以此完成对主控逻辑功能的FPGA器件EP1C6Q24017的功能重构实验验证。

图4中所有波形图的上面位置显示的均为时钟信号波形,其中图4 (a)所示是打开EPCS配置芯片写使能时,发送控制字的时序图,图中下面位置的波形为ASDO数据线上的信号,指示写使能控制字为“06”;图4(b)所示是读写使能的状态时序图,图中下面位置的波形为DATA0数据线上读取的信号,指示状态寄存器为“02”;图4(c)所示是对EPCS配置芯片进行擦除操作的时序图,图中下面位置的波形为ASDO数据线上的信号,指示擦除控制字为“C7”;图4(d)所示是读擦除操作的状态时序图,图中下面位置的波形为DATA0数据线上读取的信号,指示状态寄存器为“03”;图4(e)所示是对EPCS配置芯片进行写数据操作的时序图,图中下面位置的波形为ASDO数据线上的信号,指示写数据命令为“02”;图4(f)所示是向EPCS配置芯片传输数据过程的部分波形图,图中下面位置为ASDO数据线上的数据信号。

在满足上述时序要求的条件下,当EPCS配置芯片的数据写入完成后,FPGA即可进入配置文件所设计的工作模式,设计实验结果完全符合预期的重构目标。经过反复测试,该重构方式功能正常,能稳定地完成系统所设计的不同重构工作。

4 结束语

利用文本的方法对基于EPCS在线编程的FP-GA进行可重构设计,其硬件电路比较简单,成本低,同时不需要增加太多的硬件资源(比如大容量的存储器件等),而且配置过程灵活方便,用户只需要一个相应的配置文件数据包,即可完成系统重构功能。故此,这种FPGA的可重构设计具备广泛的应用前景。

《基于对EPCS在线编程的FPGA可重构方法》相关文章

- › 基于对EPCS在线编程的FPGA可重构方法

- 在百度中搜索相关文章:基于对EPCS在线编程的FPGA可重构方法

- 在谷歌中搜索相关文章:基于对EPCS在线编程的FPGA可重构方法

- 在soso中搜索相关文章:基于对EPCS在线编程的FPGA可重构方法

- 在搜狗中搜索相关文章:基于对EPCS在线编程的FPGA可重构方法

当前位置:

当前位置: