基于ML2035的简易正弦信号发生器设计

[11-21 23:05:23] 来源:http://www.88dzw.com 器件应用 阅读:8954次

文章摘要::范围的一个相位点。将相位寄存器的输出与相位控制字相加得到的数据作为一个地址对正弦查询表进行寻址,查询表把输入的地址相位信息映射成正弦波幅度信号,驱动DAC,输出模拟信号;低通滤波器平滑并滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。由于ML2035的控制字长为16比特,因此据DDS的原理我们不难得出ML2035的输出频率关系式为(1) 相应地,ML2035的频率分辨率(亦最小频率)为 (2) 串行数字接口ML2035的控制可以通过芯片的串行数字接口实现,数字接口部分主要由移位寄存器和数据锁存器组成。SID引脚上的16bits数据字在时钟SCK的上升沿时被送入16bits的移位寄存器。需

基于ML2035的简易正弦信号发生器设计,标签:电子小制作,电子制作网,http://www.88dzw.com:

范围的一个相位点。将相位寄存器的输出与相位控制字相加得到的数据作为一个地址对正弦查询表进行寻址,查询表把输入的地址相位信息映射成正弦波幅度信号,驱动DAC,输出模拟信号;低通滤波器平滑并滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

范围的一个相位点。将相位寄存器的输出与相位控制字相加得到的数据作为一个地址对正弦查询表进行寻址,查询表把输入的地址相位信息映射成正弦波幅度信号,驱动DAC,输出模拟信号;低通滤波器平滑并滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。由于ML2035的控制字长为16比特,因此据DDS的原理我们不难得出ML2035的输出频率关系式为

(1)

相应地,ML2035的频率分辨率(亦最小频率)为

(2)

串行数字接口

ML2035的控制可以通过芯片的串行数字接口实现,数字接口部分主要由移位寄存器和数据锁存器组成。SID引脚上的16bits数据字在时钟SCK的上升沿时被送入16bits的移位寄存器。需要注意的是,应该先送最低位,最后送最高位。然后在LAI的下降沿触发下,送入移位寄存器的数据被锁存进数据锁存器。为了确保数据的有效锁存,LAI的下降沿应该发生在SCI为“低”电平期间。同理,在SID数据移入移位寄存器期间,LAI应该保持“低”电平。

电源方式

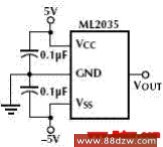

ML2035具有电源“休眠”功能,这样可以有效提高电源的使用效率,这对于便携式产品是极其有利的。当希望ML2035保持“休眠”时,可以向移位寄存器输入全“0”,并向LATI加载“1”使其保持高电平。在这种情况下,ML2035的功耗可以降到11.5mW以下,而输出正弦信号的幅度降到0V。需要提及的是,在电路设计中应该对ML2035的电源输入端进行电源去耦处理,在电路设计中可以采用如图1所示的电源去耦处理方案。

图1ML2035的电源去耦处理方法

简易正弦信号发生器设计

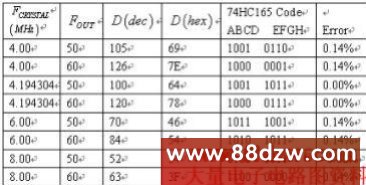

由DDS的基本原理可以知道,由于ML2035频率分辨能力有限,输出的正弦信号将有可能出现误差。对于不同的参考时钟,将产生不同程度的频率误差,表1例举了ML2035在常见的晶振下的频率控制字和频率误差情况。

表1使用常见标准晶振时ML2035所需频率控制字和频率误差情况

本文拟采用ML2035设计一简易的频率为1000Hz的高精度无频率误差的正弦信号发生器,由于低于3.5MHz的晶振通常价格较高且体积较大,故这里选用6.5536的晶振。由式(1)可以得知需要的频率控制字为1280,因此需要的16bits控制位为1111D101000000000,这样输出正弦信号的频率误差将在理论上达到0.00%。图2便是实现该简易正弦信号发生器的电路原理图,这里74HC4060计数器的功能是振荡器和计时器,而74HC4002是高速CMOS四与非门器件。为了实现ML2035的输出正弦信号频率为1000Hz,必须使在前8个脉冲移入8比特0,然后在接下来的后8个脉冲移入11111010。

Tag:器件应用,电子小制作,电子制作网,电子制作 - 器件应用

《基于ML2035的简易正弦信号发生器设计》相关文章

- › 基于ML2035的简易正弦信号发生器设计

- 在百度中搜索相关文章:基于ML2035的简易正弦信号发生器设计

- 在谷歌中搜索相关文章:基于ML2035的简易正弦信号发生器设计

- 在soso中搜索相关文章:基于ML2035的简易正弦信号发生器设计

- 在搜狗中搜索相关文章:基于ML2035的简易正弦信号发生器设计

编辑推荐

最新更新

热门排行

- ・ 电力线载波通信(LMl893)集成电路

- ・ 基于ML2035的简易正弦信号发生器设计

- ・ LM317参数与中文使用手册

- ・ 单节锂电池充电管理集成电路LP3947

- ・ 延时关灯器

- ・ 压力传感器

- ・ 压敏电阻原理概述

- ・ 停电自锁保护开关

- ・ 音调解码567详解

- ・ 整流电源的过压保护

当前位置:

当前位置: