高速HDI电路板设计过程的考虑(推荐)

[08-09 20:40:07] 来源:http://www.88dzw.com CAD CAM 阅读:8653次

文章摘要:Fig 1-2 封装用的高密度IC基板 1.3 高层数HDI产品 高层数HDI板通常是第1层到第2层或第1层到第3层有激光钻孔的传统多层板。采用必须的顺序叠层工艺,在玻璃增强材料上进行微孔加工是另一特点。该技术的目的是预留足够的元件空间以确保要求的阻抗水平。图1-3描述了该类典型的多层板结构。 该技术适用于拥有高I/O数或细间距元件的高层数HDI板,埋孔工艺在该类产品中并非是必要工艺,微孔工艺的目的仅仅在于形成高密度器件(如高I/O元件、uBGA)间的间距,HDI产品的介电材料可以是背胶铜箔(RCF)或者半固化片(prepreg)。 Fig 1-3 高性能产品的高层数板 2.

高速HDI电路板设计过程的考虑(推荐),标签:CAD教程,CAM资料,http://www.88dzw.comFig 1-2 封装用的高密度IC基板

1.3 高层数HDI产品

高层数HDI板通常是第1层到第2层或第1层到第3层有激光钻孔的传统多层板。采用必须的顺序叠层工艺,在玻璃增强材料上进行微孔加工是另一特点。该技术的目的是预留足够的元件空间以确保要求的阻抗水平。图1-3描述了该类典型的多层板结构。

该技术适用于拥有高I/O数或细间距元件的高层数HDI板,埋孔工艺在该类产品中并非是必要工艺,微孔工艺的目的仅仅在于形成高密度器件(如高I/O元件、uBGA)间的间距,HDI产品的介电材料可以是背胶铜箔(RCF)或者半固化片(prepreg)。

Fig 1-3 高性能产品的高层数板

2. 高性能产品平台

高性能HDI产品的发展有5个主要驱动因素必须予以考虑,这几个因素相互交替作用。这些因素分别是:

电路(信号完整性)

元件

基材

叠层与设计规则

组装过程的考虑

设计这种带微孔的印制电路板是非常复杂的任务,虽然电路由于考虑了信号完整性显得极为重要的,但是成本的因素也不容忽视。基于此,实际操作中必须考虑折中的方案。

2.1 电路(信号完整性)考虑

实际电路的性能因信号上升时间的不同而有所差别,由于这些面积较大、性能要求较高的HDI板处理的是高速的计算机总线或电信信号,它们对于噪声和信号反射非常敏感。以下5个最本质的特性可描述出信号的敏感度:

特性阻抗

低压差分信号(LVDS)

信号衰减

噪音敏感度

串音干扰

信号完整性因素

单端的微带线、带状线、共面和差分信号的特性阻抗是由基材的介电常数、板厚、层叠结构、设计规则共同决定的。信号的衰减是材料的介电损耗、设计规则和线路长度共同作用的结果。包括串扰在内的各种噪音如: 地平面反弹噪声(ground bounce) ,开关噪声(switching noise),电源峰值噪声(Power supply spikes)等,则是由板的叠层结构确定的电源耦合、地层、设计规则和原材料特性共同作用的结果。

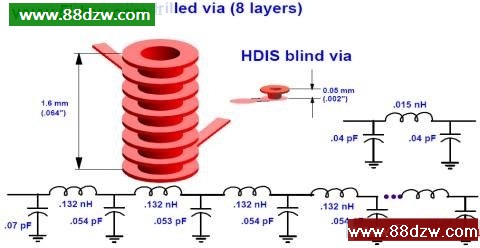

改善高速信号板的信号完整性的一个主要目标就是降低电感。低电感值的SMT 焊盘通常是那些没有走线或采用 VIP (Via-in-pad)工艺的焊盘。图2-1说明一个微孔的电感和电容值仅是一个标准通孔的十分之一左右。

Fig2-1 通孔与微孔的电气性能比较

2.2 元件的考虑

高I/O数、细间距的BGA和uBGA技术日新月异,这些技术的普遍使用正是微孔工艺在这些面积较大的多层板中得到广泛采用的重要原因。即使器件采用更精细的1.0或0.8mm的间距,由于I/O数量的不断增加,元件依然很大,这就增加信号线布线的难度。一些大而复杂的BGA就通过采用共熔(co-fired)陶瓷基板来解决这些问题,如果一边的陶瓷快接近32-34mm的时候,焊料柱将替代焊料球。如下因素将影响设计:

SMT间距

I/O数

- 上一篇:PCB尺寸和外形的设计

《高速HDI电路板设计过程的考虑(推荐)》相关文章

- › 高速HDI电路板设计过程的考虑(推荐)

- 在百度中搜索相关文章:高速HDI电路板设计过程的考虑(推荐)

- 在谷歌中搜索相关文章:高速HDI电路板设计过程的考虑(推荐)

- 在soso中搜索相关文章:高速HDI电路板设计过程的考虑(推荐)

- 在搜狗中搜索相关文章:高速HDI电路板设计过程的考虑(推荐)

当前位置:

当前位置: